FIFO最小深度计算

1、FIFO最小深度

在数据的传输中当读速率慢于写速率时,FIFO便可被用作系统中的缓冲元件或队列,类似于水流经过一个缓冲区,上游水流速度快,下游水流速度慢,部分水就可以被缓存在中间的缓冲区,但是上游与下游的水速差距过大,就会导致流入中间缓存区的水超出了缓存区承受能力导致水的溢出,不能顺利到达下游。在上游水流速度最大,下游水流速度最小的情况下,中间缓冲区不能溢出的大小就是我们关系的问题。

同理,读写速率差距过大,FIFO深度太小,就会导致一段时间内向FIFO灌输的数据超出了FIFO的承受能力,就会导致数据的丢失,该容量取决于读写数据的速率。所以在写速率最大,读速率最小时,这时正好不导致数据溢出的FIFO的深度就是我们要计算的FIFO最小深度。

FIFO写入速率快,读出速度慢模型:

最简单的写快读慢的实例,FIFO写入一个数据需要1s,读取一个数据需要2s,一共传输6个数据。(下图)

6个数据写入需要时间为:6×1=6 s

6s读取的数据为:6/2=3个

6s FIFO内剩余数据的个数:6-3=3个

6s才能读取3个数据,剩余的数据3个在FIFO中缓冲,在6s的之后的时间才能被缓慢读出。

仔细观察下图(写快读慢),FIFO中最多存在3个数据,该容量就是FIFO的最小深度。

该FIFO的最小深度 = 6 - 3 = 3(如果深度小于3,则会导致数据丢失)。

总结:要确定FIFO的深度,关键在于计算出在突发读写的这段时间内有多少数据没有被读走。也就是说FIFO的最小深度就等于没有被读走的数据个数。

FIFO写入与读取速度相同:

读数据速率比写数据快,因此FIFO只起到变换时钟域的作用,FIFO最下深度为1即可。

2、示例分析

示例一:

写入速率 > 读取速率

A/D采样率为50MHz,读A/D的速率为40MHZ,要不丢失地将10万个采样数据送入FPGA,在A/D和FPGA之间至少加多大容量(深度)的FIFO才可以?

写一个数据所需的时间为:

1

/

50

M

H

z

=

0.02

×

1

0

−

6

s

1/50MHz=0.02×{10^{ - 6}}s

1/50MHz=0.02×10−6s

写完所有的数据所需的时间为:

100

,

000

×

0.02

×

1

0

−

6

=

0.002

s

100,000×0.02×{10^{ - 6}} = 0.002s

100,000×0.02×10−6=0.002s

读一个数据所需的时间为:

1

/

40

M

H

z

=

0.025

×

1

0

−

6

s

1/40MHz=0.025×{10^{ - 6}} s

1/40MHz=0.025×10−6s

0.002S内读走的数据为:

0.002

/

(

0.025

×

1

0

−

6

)

=

0.08

×

1

0

6

=

80

,

000

0.002/(0.025×{10^{ - 6}}) = 0.08×{10^{ 6}} = 80,000

0.002/(0.025×10−6)=0.08×106=80,000

则FIFO的最小深度为:

100

,

000

−

80

,

000

=

20

,

000

(

0.002

s

还

没

有

被

读

走

的

数

据

的

个

数

)

100,000 - 80,000=20,000(0.002s还没有被读走的数据的个数)

100,000−80,000=20,000(0.002s还没有被读走的数据的个数)

(如果读比写慢几拍,则深度比20,000略大)

示例二:

FIFO写入时钟为100MHz,读取时钟为80Mhz,分以下情况分析。

①:传输2000个数据,FIFO最小深度为多少?

100MHz时钟写入一个数据需要的时间为

1

/

100

M

H

z

=

10

n

s

1/100MHz=10ns

1/100MHz=10ns

写入2000个数据所需的时间为

2000

×

10

=

20000

n

s

2000×10=20000ns

2000×10=20000ns

80MHz时钟读出一个数据所需的时钟

1

/

80

M

H

z

=

12.5

n

s

1/80MHz=12.5ns

1/80MHz=12.5ns

20000ns读出的数据个数为

20000

n

s

/

12.5

n

s

=

1600

20000ns / 12.5ns=1600

20000ns/12.5ns=1600

剩余FIFO中没读走的数据个数为

2000

−

1600

=

400

2000-1600=400

2000−1600=400

所以FIFO的最小深度为400。

②:100个时钟写入80个数据,1个时钟读1个数据,求FIFO的最小深度

100MHz时钟写入一个数据需要的时间为

1

/

100

M

H

z

=

10

n

s

1/100MHz=10ns

1/100MHz=10ns

80MHz时钟读出一个数据所需的时钟

1

/

80

M

H

z

=

12.5

n

s

1/80MHz=12.5ns

1/80MHz=12.5ns

100个时钟写入80个数据,可以以下理解,100个时钟包含80个有效写时钟,20个空闲时钟。

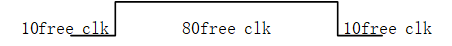

但是在什么情况下会出现突发写入数据最多呢,在两个100个时钟,前一个100个时钟的后80个时钟在写数据,后100个时钟的前80个数据在写数据,也就是如下所示:

在这种情况下,以100MHz的时钟一次写入了160个数据。

写入160个数据所需的时间为

160

×

10

n

s

=

1600

n

s

160×10ns=1600ns

160×10ns=1600ns

1600ns读取的数据个数为

1600

n

s

/

12.5

n

s

=

128

1600ns/12.5ns=128

1600ns/12.5ns=128

FIFO内剩余的数据为

160

−

128

=

32

160-128=32

160−128=32

所以FIFO最小深度为32

③:100个时钟写入80个数据,3个时钟读1个数据,求FIFO的最小深度

100MHz时钟写入一个数据需要的时间为

1

/

100

M

H

z

=

10

n

s

1/100MHz=10ns

1/100MHz=10ns

80MHz时钟读出一个数据所需的时钟

(

1

/

80

M

H

z

)

×

3

=

12.5

×

3

n

s

(1/80MHz)×3=12.5×3ns

(1/80MHz)×3=12.5×3ns

100个时钟写入80个数据,可以以下理解,100个时钟包含80个有效写时钟,20个空闲时钟。

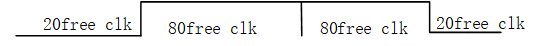

但是在什么情况下会出现突发写入数据最多呢,在两个100个时钟,前一个100个时钟的后80个时钟在写数据,后100个时钟的前80个数据在写数据,也就是如下所示:

在这种情况下,以100MHz的时钟一次写入了160个数据。

写入160个数据所需的时间为

160

×

10

n

s

=

1600

n

s

160×10ns=1600ns

160×10ns=1600ns

1600ns读取的数据个数为

1600

n

s

/

(

12.5

×

3

)

n

s

=

42.66

1600ns/(12.5×3)ns=42.66

1600ns/(12.5×3)ns=42.66

FIFO内剩余的数据为

160

−

42.66

=

117.33

160-42.66=117.33

160−42.66=117.33

所以FIFO最小深度为118(FIFO一般设置为2的n次幂(128))。

④:100个时钟写入80个数据,3个时钟读2个数据,求FIFO的最小深度

100MHz时钟写入一个数据需要的时间为

1

/

100

M

H

z

=

10

n

s

1/100MHz=10ns

1/100MHz=10ns

80MHz时钟读出一个数据所需的时钟

(

1

/

80

M

H

z

)

×

3

/

2

=

12.5

×

3

/

2

n

s

(1/80MHz)×3/2=12.5×3/2ns

(1/80MHz)×3/2=12.5×3/2ns

100个时钟写入80个数据,可以以下理解,100个时钟包含80个有效写时钟,20个空闲时钟。

但是在什么情况下会出现突发写入数据最多呢,在两个100个时钟,前一个100个时钟的后80个时钟在写数据,后100个时钟的前80个数据在写数据,也就是如下所示:

在这种情况下,以100MHz的时钟一次写入了160个数据。

写入160个数据所需的时间为

160

×

10

n

s

=

1600

n

s

160×10ns=1600ns

160×10ns=1600ns

1600ns读取的数据个数为

1600

n

s

/

(

12.5

×

3

/

2

n

s

)

n

s

=

85.33

1600ns/(12.5×3/2ns)ns=85.33

1600ns/(12.5×3/2ns)ns=85.33

FIFO内剩余的数据为

160

−

42.66

=

74.66

160-42.66=74.66

160−42.66=74.66

所以FIFO最小深度为75(FIFO一般设置为2的n次幂(128))。

★★★如有错误,欢迎指导!!!