今天要给大家介绍的数字后端基本概念是Track。Track是指走线轨道,和row一样,可以约束走线器的走线方向。信号线通常必须走在track上。Std Cell的高度通常用metal2 track pitch来表示,常用的 std cell 库有 7T /9T /12T,就是以 track 来区分的, 9T 就是说 std cell 的高度范围内可以走九条线,所以一般来讲, 7T cell 的 size 最小, 9T cell 的 size 稍大。

下图中五颜六色的线条就是每层layer上定义的track走线轨道

通常我们在design的technology lef中定义Track的属性,如下图所示:

LAYER M1

TYPE ROUTING ;

DIRECTION VERTICAL ;

PITCH 0.090 0.064;

OFFSET 0.000 0.000;

MAXWIDTH 2 ;

WIDTH 0.032 ;

上述M1 layer的定义中,TYPE ROUTING代表这是一层走线层,我们还有其他的type包括Implant,Masterslice等。

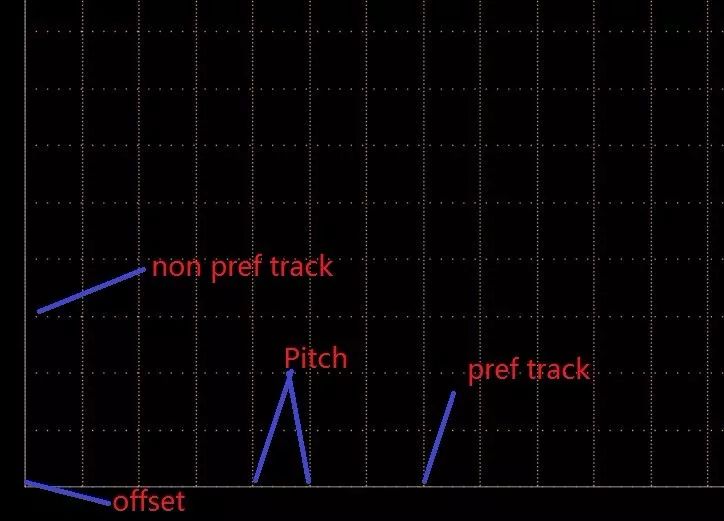

DIRECTION代表这层Metal prefer走线方向,这边值得注意的是,每层track会分为pref track和non pref track。pref track就是这层layer上主流的走线方向,那剩下的non pref track就是非主流方向。因此上述例子中的主流走线方向就是vertical(纵向),非主流就是横向(honrizontal)。通常。走non-pref track的wire会比较宽,这样就比较占用绕线资源。所以,一般不推荐使用non-pref track。特别是在先进工艺的设计中,绕线资源极其紧张,一般很少用到non-pref track.

PITCH就是每条track之间的间距,上述例子中,垂直方向间距是0.09,水平方向是0.064.

OFFSET就是第一条track偏离起始点的距离

WIDTH就代表默认这层layer上wire的宽度,MAXWIDTH就代表最高不能超过多少width

1. track, site, row有什么区别,分别会对cell属性产生什么影响?

2. 为什么wire和pin 需要走在track上,偏离了会有什么坏处?