Introduction

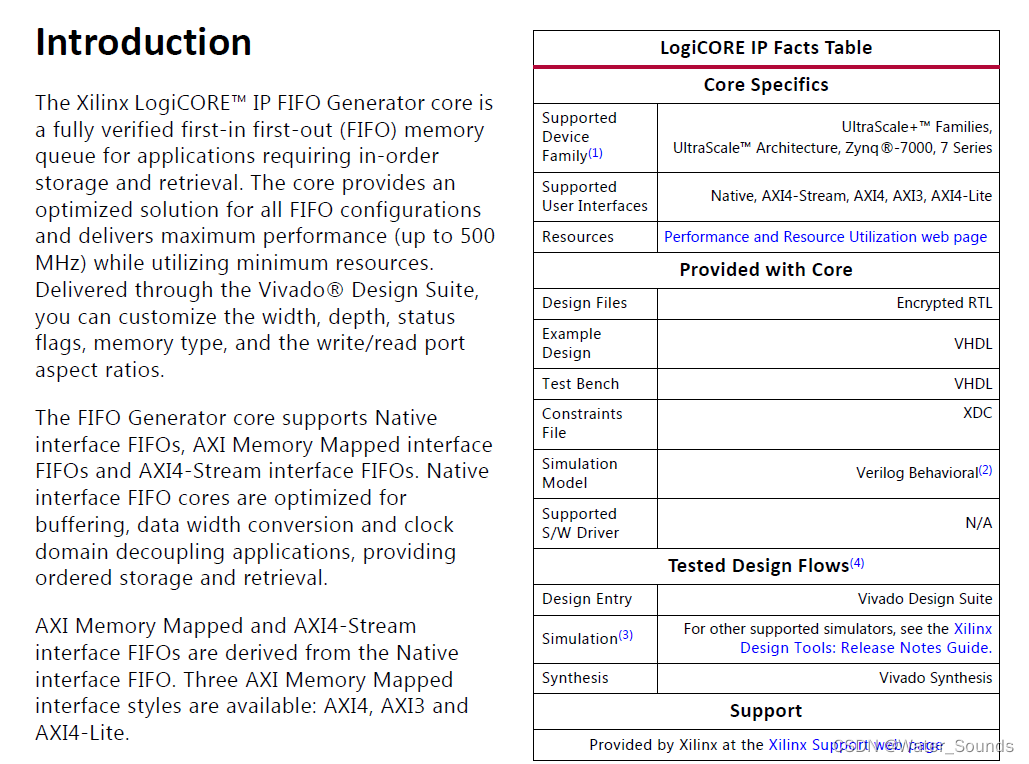

该核心为所有FIFO配置提供了优化的解决方案,并在利用最少资源的同时提供了最大性能(高达500 MHz)。

FIFO IP核提供本地接口、AXI内存映射接口和AXI4流接口 FIFO。本地接口为缓冲、数据位宽转换和时钟域去耦等应用提供最优方案,支持有序的存储和检索。

AXI内存映射接口和AXI4流接口源自从本地接口FIFO,前者支持AXI4, AXI3和AXI4-Lite三种类型。

AXI为一种协议,是一种标准化的总线接口,线多,操作复杂,常用的还是Native FIFO。

可看到,Introduction部分介绍的非常笼统,从很大的方向上讲明FIFO是什么。

Ch. 1: Overview

概述,和Introduction中的内容差不多,指明:FIFO的使用场景、最大时钟、支持的接口类型以及在VIVADO中使用时,需要配套,包括读取、写入指针和状态标志的生成等逻辑。

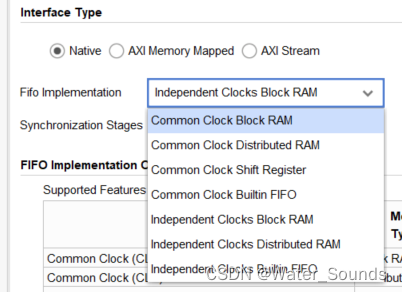

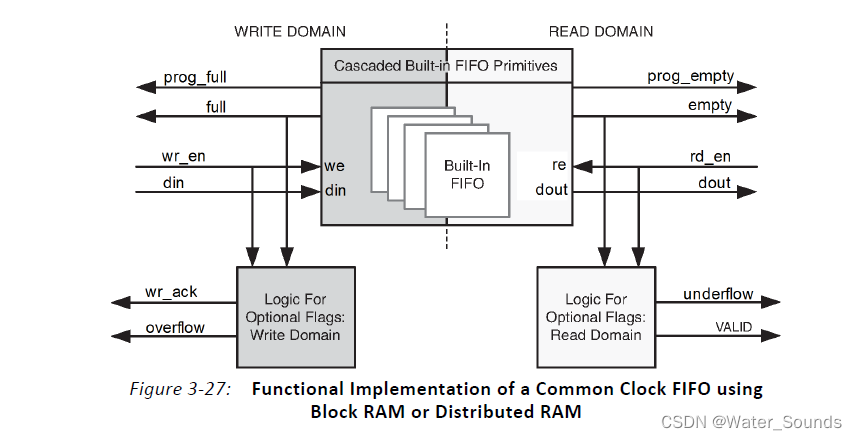

本地接口FIFO可以使用块RAM,分布式RAM或某些FPGA系列中可用的内置FIFO资源来创建高性能、区域优化的FPGA设计。

本地接口FIFO支持标准模式和首字直通(First Word Fall Through)(FWFT)两种操作模式,后者可以不需要读命令,自动的将最新数据放在dout上,相当于数据输入进去就会漏出来。

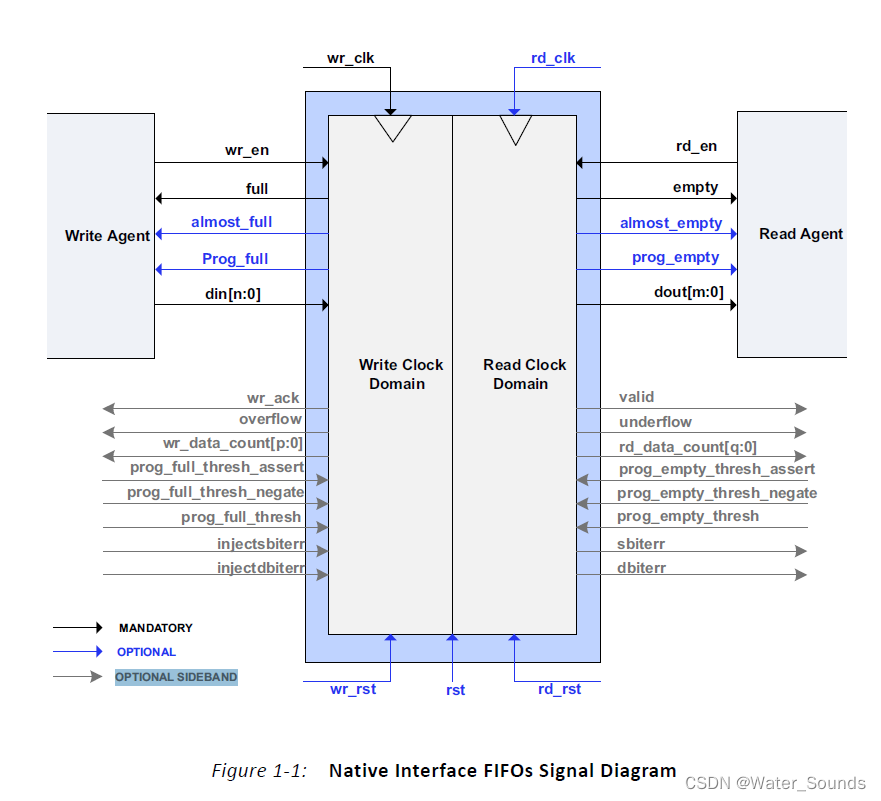

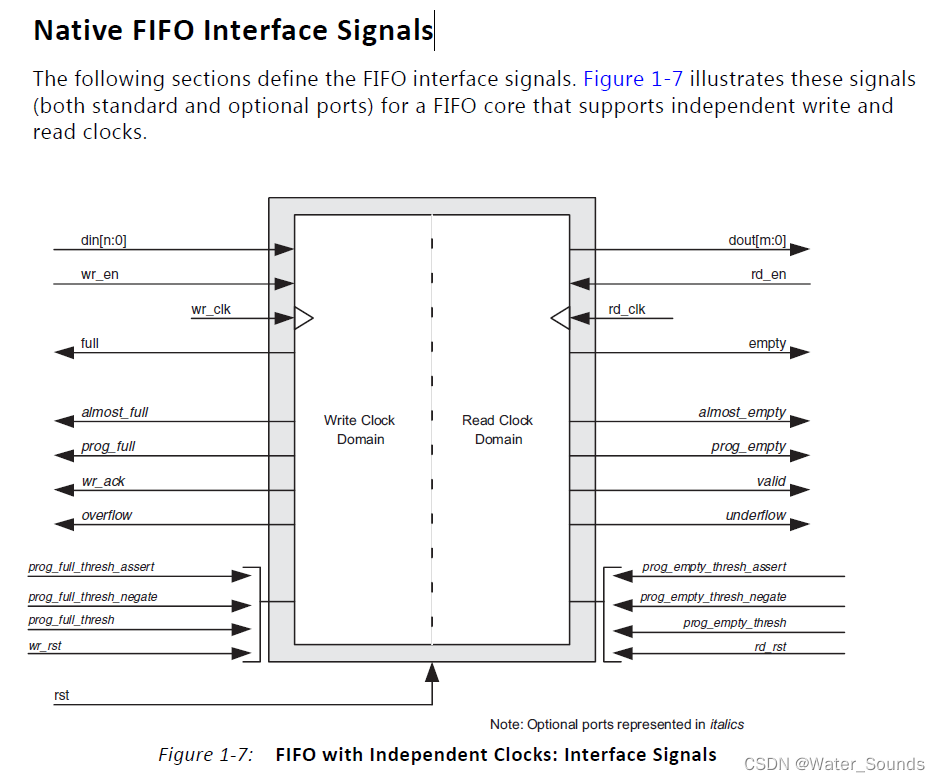

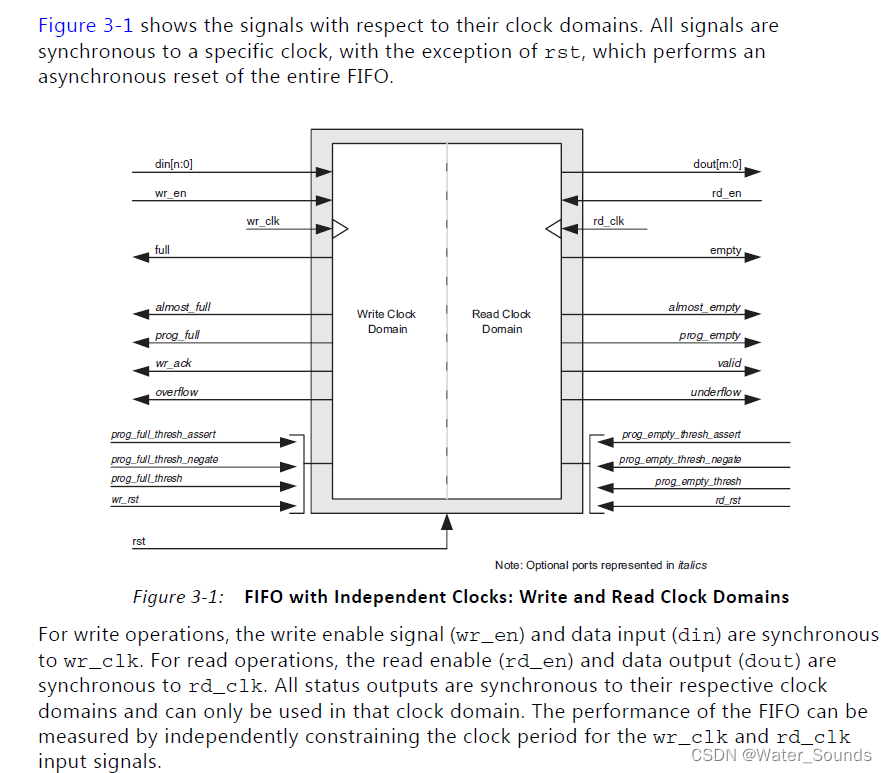

黑色为强制保留端口,蓝色为可选端口,灰色为可选边带端口。故黑色应为最重要端口,可见FIFO分为写时钟和读时钟两个区域,分别对应外部的写和读。

(跳过AXI接口FIFO的overview)

Feature Summary

Feature Summary中首先介绍了共同的功能

Feature Summary中首先介绍了共同的功能

- 支持各种各样的接口

- 深度最大到131072字

- 读写时钟域可以独立可以一样

- VHDL演示了演示了IP核心的设计流程,包括如何实例化和模拟它(学的Verilog,还有参考价值吗?)

- 使用Xilinx Vivado IP目录自定义程序进行完全配置(VIvado里可以用就是了)

Native FIFO特定功能:

- 支持的位宽1~1024

- 对称或非对称纵横比(读写端口比范围从1:8到8:1),说白了就是输入输出位宽的比例,最大比例是8

- 同步或者异步复位选项

- 可以灵活的选择存储资源类型

- 支持标准模式和首字直通(First Word Fall Through)(FWFT)两种操作模式

- Full和Empty状态标志,以及用于指示还剩一个单词的Almost Full和Almost Empty标志

- 可编程的满和空状态标志,由用户定义的常量或专用输入端口设置

- 可配置的握手信号

- Hamming错误注入和校正检查(ECC)支持块RAM和内置FIFO配置

- 块RAM FIFO的软ECC支持(高达64位数据宽度)

- 块RAM和内置FIFO配置的嵌入式寄存器选项

- UltraScale的动态电源门控和ECC流水线寄存器支持™ 体系结构内置FIFO配置

上述的各种支持功能,常用性应该也是前边的几个,后边的配置,暂时基本上接触不上,人家毕竟做手册,写的全是他的事儿,怎么看是咱的事儿。

接下来手册里进一步介绍了如上12种功能的具体内容,把一句话扩展成一段话,对哪个功能感兴趣可以再去看,Native FIFO Interface Signals这节应该好好看一下。

Native FIFO Interface Signals

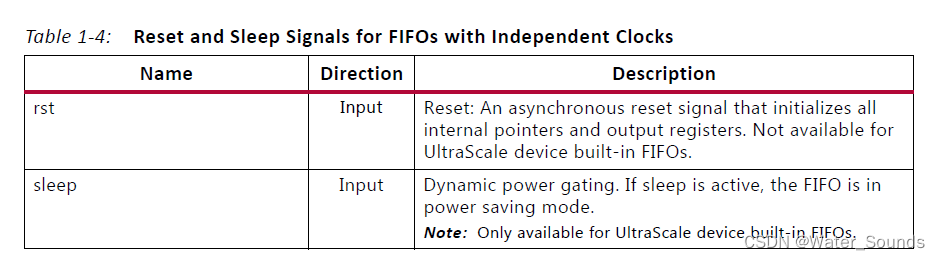

rst 为复位输入端口,一种异步复位信号,用于初始化所有内部指针和输出寄存器。不适用于UltraScale设备内置的FIFO

sleep 仅适用于UltraScale设备内置的FIFO

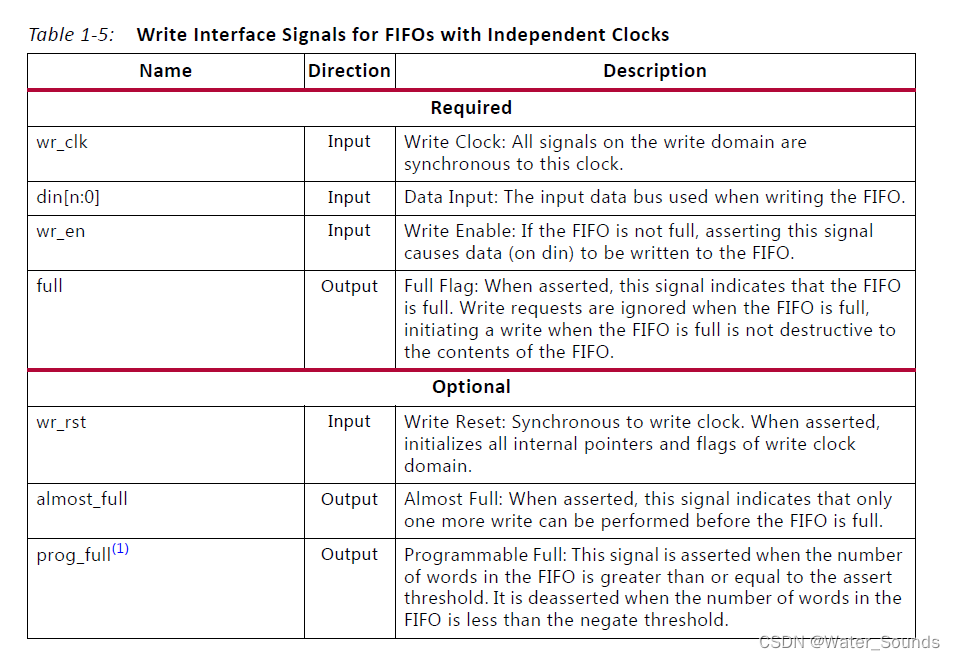

首先来看写端的端口,表格1-5按照必须和可选划分

必须的:

wr_clk-写时钟:写入域上的所有信号都与该时钟同步

din[n:0]-输入数据:接入的数据

wr_en-写使能:如果FIFO未满,置位该信号将把din的数据写入FIFO

full-写满信号:它被置位时,说明FIFO已经写满了,FIFO将不再理会后续的写使能信号,直接自闭,保持里面的数据不动。

(此处为什么说置位而不是拉高拉低呢?手册中用asserted,说明它是可以配置的,高有效、低有效都行)

可选的:

wr_rst Input-写复位:同步在写时钟上的信号,当它置位时,初始化写入时钟域的所有内部指针和标志。

almost_full-几乎满:当置位时,标志着再写一个,就得满了,就差那么一个。

prog_full-可编程满:自己设置一个阈值,大于等于阈值就是满,该信号就会被置位,小于阈值就不会置位。

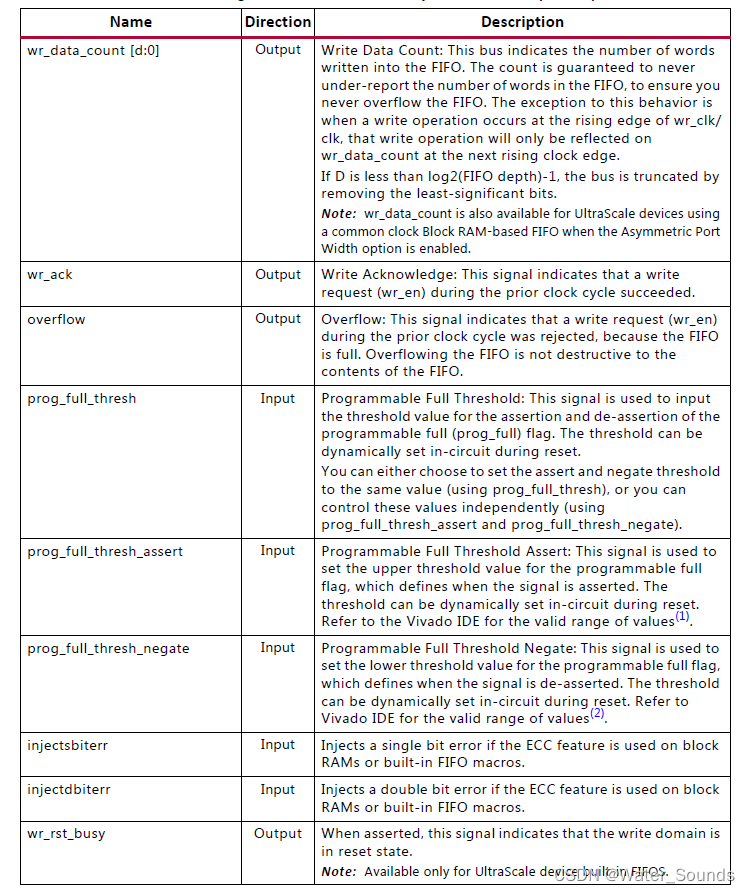

wr_data_count [d:0]-写入数据计数:它输出的是已经写入FIFO的数据字数,该计数保证永远不会低估FIFO中的字数,以确保您永远不会溢出FIFO。这种行为的例外是,当写入操作发生在wr_clk/clk的上升沿时,该写入操作将仅反映在下一个上升时钟沿的wr_data_count,意思为,该时钟写入,至少下个时钟才能实现wr_data_count++,差了一个时钟。

其余的跳过。

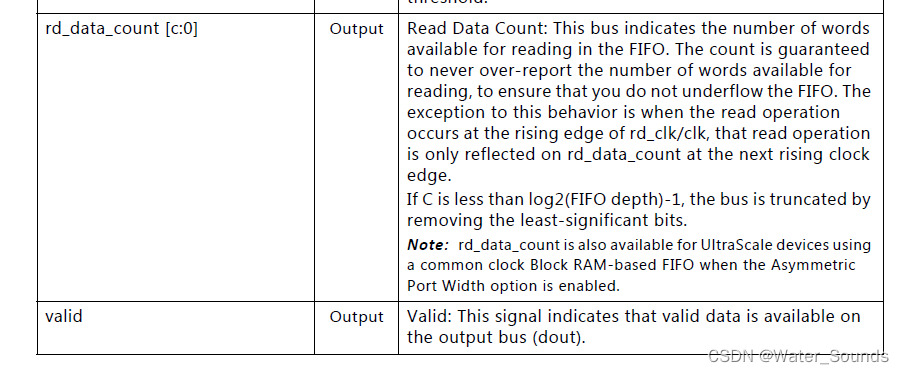

读端口大部分和写端口同理,重点介绍下面两个端口功能。 rd_data_count [c:0]-读计数:指示FIFO中可供读取的字数。计数保证永远不会过度报告可供读取的字数,以确保FIFO不会下溢(榨干),这种行为的例外是,当读取操作发生在rd_clk/clk的上升沿时,该读取操作仅反映在下一个上升时钟沿的rd_data_count上,也就是你在一时钟处进行读操作时,下一个时钟才能完成rd_data_count- -的操作。

rd_data_count [c:0]-读计数:指示FIFO中可供读取的字数。计数保证永远不会过度报告可供读取的字数,以确保FIFO不会下溢(榨干),这种行为的例外是,当读取操作发生在rd_clk/clk的上升沿时,该读取操作仅反映在下一个上升时钟沿的rd_data_count上,也就是你在一时钟处进行读操作时,下一个时钟才能完成rd_data_count- -的操作。

该端口需要注意,它不是代表从FIFO中已经读出的数据计数(done),而是FIFO中可以读出来的数据计数(to do),它的计数从empty拉低开始

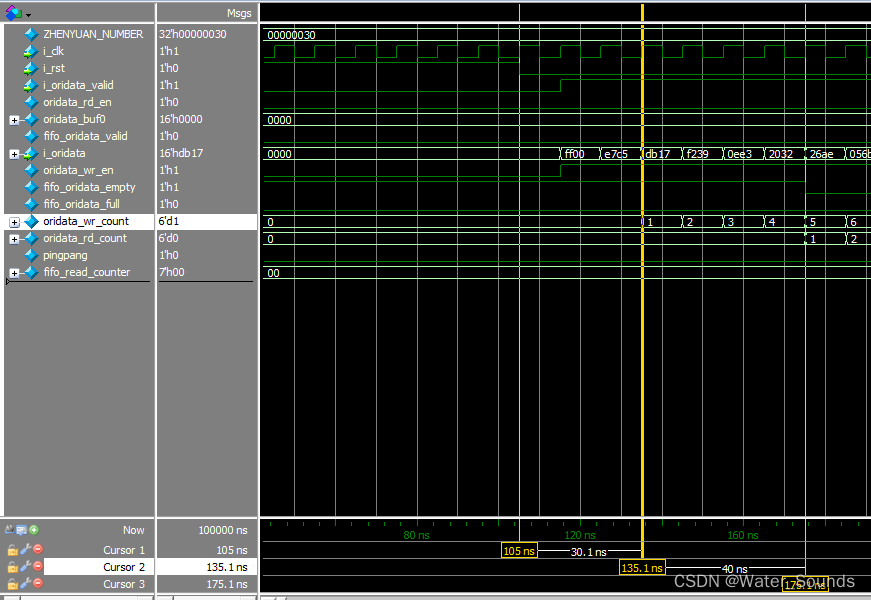

如上图,复位信号拉低后,经过1clk后,写使能拉高,数据开始写入FIFO,再经过2clk,wr_count开始计数,empty信号拉低后,rd_cout信号开始计数,但是注意光标时间,wr_count和rd_count两个信号并不是和clk时钟信号对齐的。(这个问题。。。。应该是IP核的固有问题?)

Applications

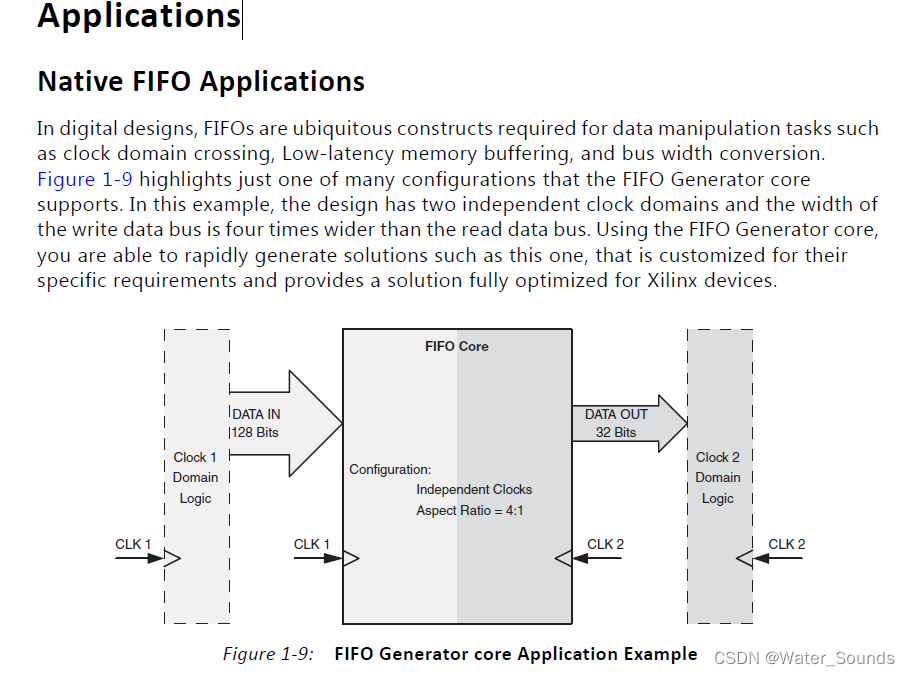

Native FIFO Applications

介绍了一个FIFO的典型应用,指导意义有限。

至此,Overview看了个大概,总结来说,该章中主要介绍IP核的应用场景、适配性等问题,并会给出IP核接口的详细说明,还会有简略的时序图说明接口之间的关系,力求全面总体,后面的章节一定是对ch1中提到的多有功能做出系统的详细的说明。

Ch. 2: Product Specification

本章包括有关性能和延迟的详细信息。本章中各种指针向其他文章,不想看。

Ch. 3: Designing with the Core

本章应该比较重要,一个⭐,一个IMPORTANT,说明开发者要严格遵守下面章节的内容设计。

General Design Guidelines

官方手册真是那个啊,上来让评估设计难度,真他娘的专业,主要从:最大时钟频率、目标设备架构(接口类型?)和特定用户功能三方面考虑,确保使用设计技术来促进实施,包括流水线和使用约束(时间约束、放置和/或面积约束)。

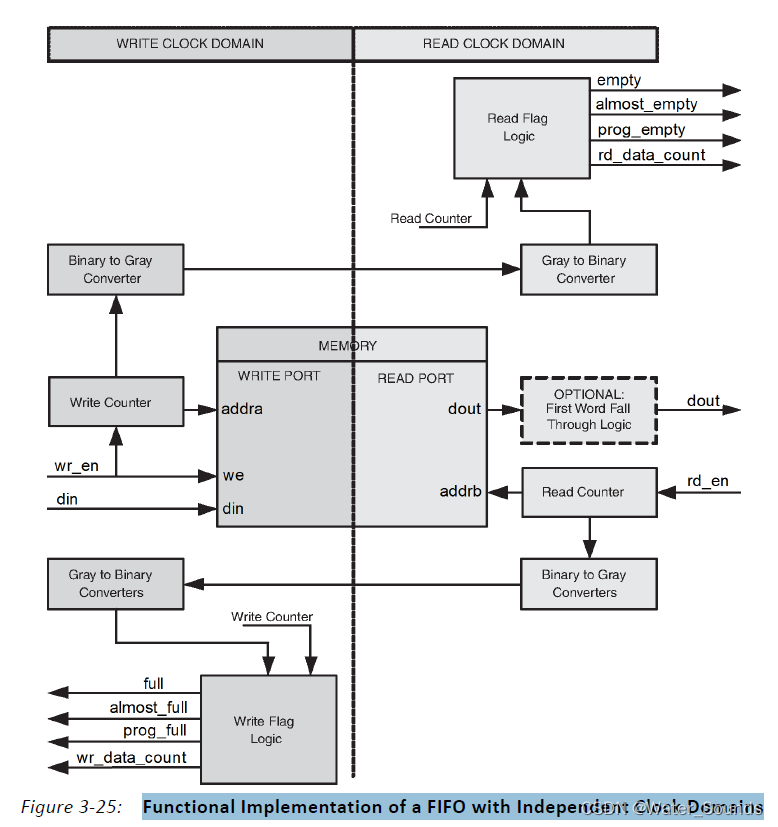

接下来了解信号管道化和同步,为了理解FIFO设计的本质,了解如何使用流水线来最大限度地提高性能,并实现时钟域交叉的同步逻辑是很重要的。写入din接口的数据可能需要多个时钟周期才能在读取接口上访问。

感觉略抽象,对于时序的前考虑有点困难。

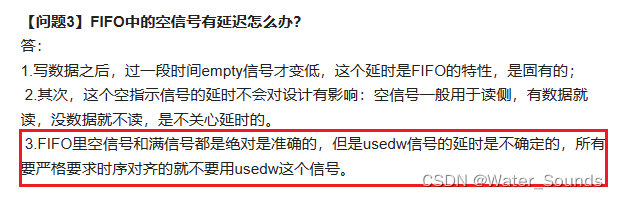

同步的注意事项: 必须使用FIFO Full和Empty标志来保证正确的行为。

图3-1中给出了所有和时钟有关的信号,rst除外,它是异步复位信号。除了写使能、写数据两个口,所有输出的状态信号,都严格同步于其所在的时钟域,且只能在其所在的时钟域使用,观察图中,并没有wr_cout和rd_count信号,对应Native FIFO Interface Signals最后一段提到的,这两个计数信号并不会同步于所在的时钟。

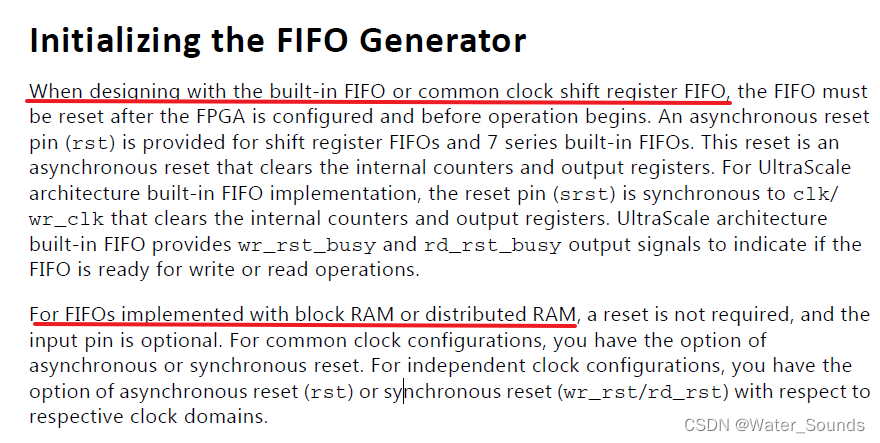

Initializing the FIFO Generator

下划线的对应两种设计模式,不同的设计模式对复位的要求是不同的。

对于用块RAM或分布式RAM实现的FIFO,不需要复位,输入引脚是可选的。对于常见的时钟配置,可以选择异步或同步复位。对于独立的时钟配置,您可以选择异步复位(rst)或同步复位(wr_rst/rd_rst),分别针对各自的时钟域。

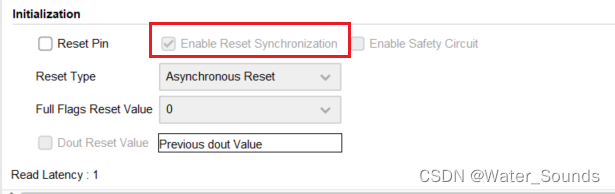

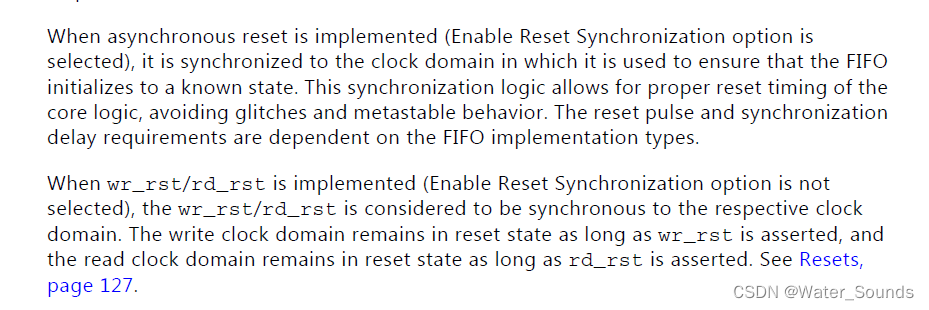

这个选项是否勾选,手册中介绍:

总之,勾选的话,执行异步复位时,rst置位,它将同步到用于确保FIFO初始化为已知状态的时钟域(?);不勾选的话,只要wr_rst被置位,写时钟域就保持复位状态,只要rd_rst被置位,读时钟域就会保持复位状态。(是否使用前者更好?)

FIFO Usage and Control(重要)

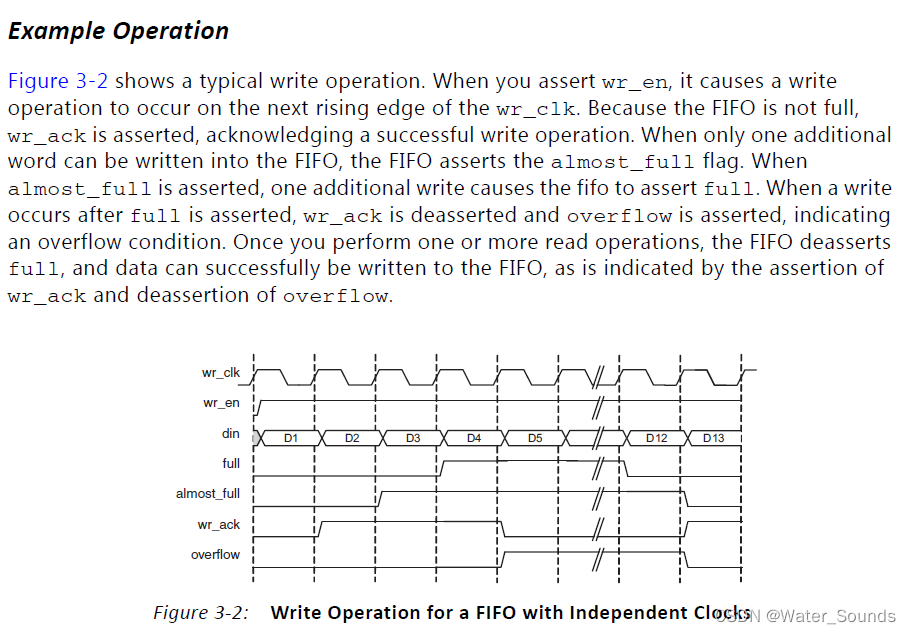

这段话把写入过程中的逻辑说的很清楚,当FIFO不full且wr_en信号拉高时,din数据写入,同时wr_ack也会置位,wr_ack表示:

如果一直不读,FIFO早晚被写满,满了之后,就会忽略wr_en的写请求,且保持内部数据不变,同时拉高溢出信号(overflow flag)。

官方给出了一个实例,值得认真参阅

下面是读操作。

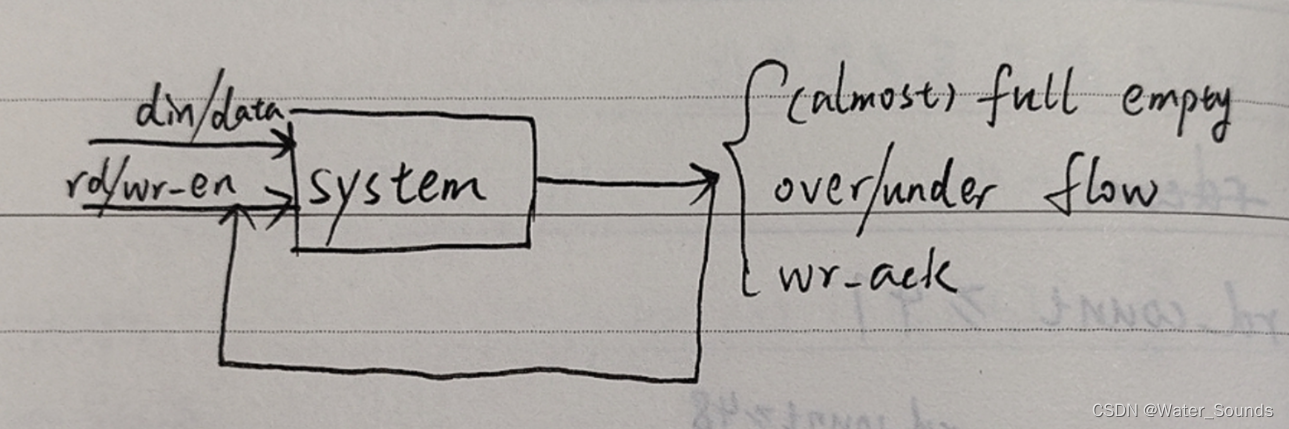

上图把读过程中的几个关键信号逻辑讲的很明白。突然有点理解状态信号的含义,读写使能信号是被控制的量,相当于一个系统的输出,而状态信号如full、empty、almost系列、上溢、下溢等,都是一个系统的输入,而这个输入输出关系,在IP核的端口层面来看,又是反过来的。这个system,就是我们要配套FIFO编写的逻辑,用flag去控制en。

下面介绍了两种读取模式,FWFT应该也比较常用,但是暂时用不上。

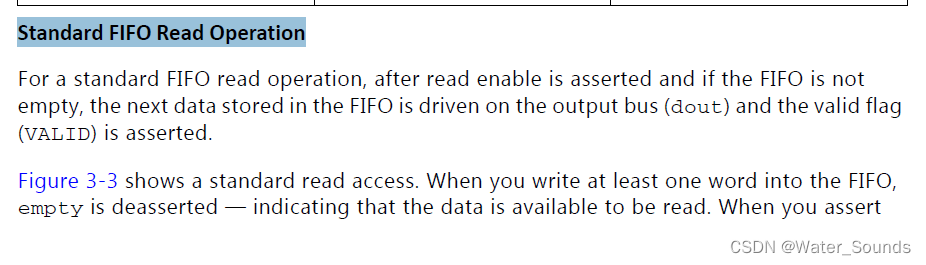

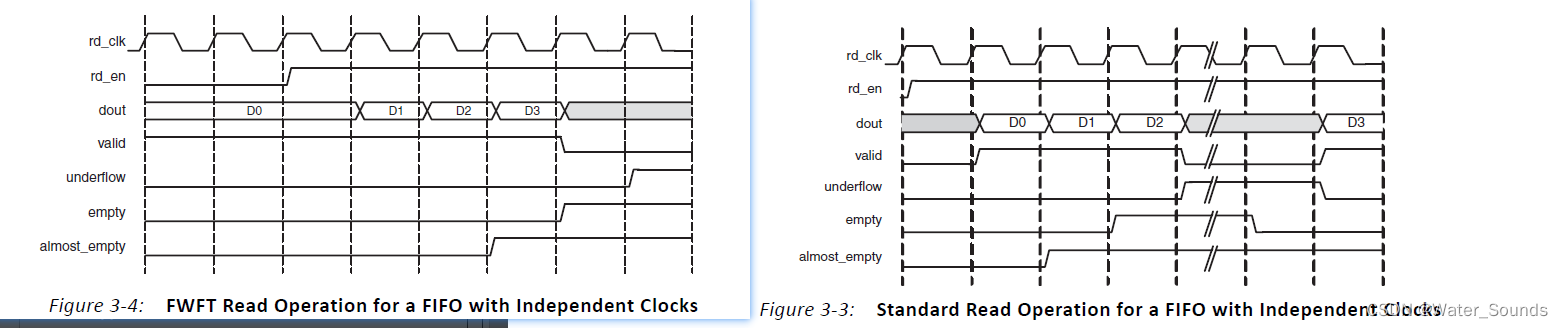

第一种:Standard FIFO Read Operation

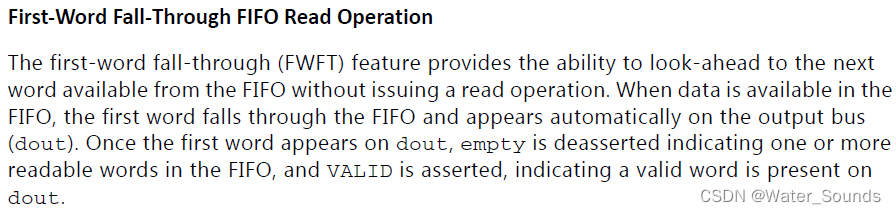

第二种:First-Word Fall-Through FIFO Read Operation

对比一下,第二种模式的empty信号和underflow信号都比第一种延后1clk。

Clocking

Reset

讲了同步复位和异步复位的概念。

Latency