第5章 波形发生器软件设计

本章我们将介绍系统的软件设计。系统中控制软件占有很重要的地位。它不仅要产生波形数据,控制波形的发生,还要控制显示电路和键盘电路,因此系统软件的好坏直接决定着系统的功能和稳定。

5.1软件的总体结构

在本系统中,由于要求产生四种不同的基本函数波形,所以系统软件的设计占用了较多的时间和精力。

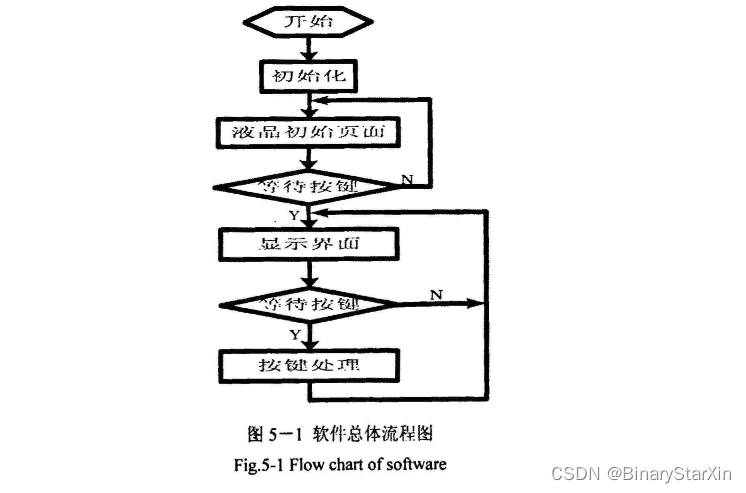

整个系统的主程序的流程图如图5-1所示整个程序分成初始化子程序、显示界面子程序、等待按键子程序、按键处理子程序等四大部分组成,其中按键处理子程序又划分成几个分模块来实现。其中系统的初始化包括单片机的初始化、液品控制器的初始化。显示界面主要实现波形发生器的频率显示和波形显示。其他的几个模块将在下面的章节做详细的介绍。

5.2软件的分模块设计

在初始化完成后,系统将显示液品的初始页面,表示系统工作正常,等待用户的操作命令,在用户按下任意键后,系统将进入显示界面。 系统的按键界面设计如图5-2。其中方波键、正弦波键、三角波键、锯齿波键、任意波键用来选择波形。C键为清零键。MHZ 键、KHZ键和HZ键为频率单位,用来指定输入的频率单位。占空比高键和占空比低键用来控制方波的占空比。“确定”键在设置好频率和波形后,按下此键系统就将按用户的设置输出波形。