很多人纠结FPGA和IC设计怎么选,其实往小了说,要看你选择的具体是哪个方向岗位。往大了说,将来你要是走更远,要成为大佬,那基本各个方向的都要有涉及的。

不同方向就有不同的发展,目前在薪资上IC设计要比FPGA要高一点(但每个行业都有大佬,薪资还是有一定的差别)。

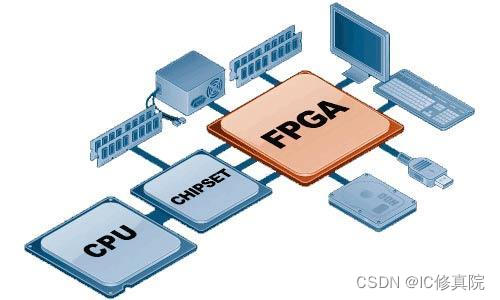

这里就来看看FPGA和IC设计的ASIC

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

它是当今数字系统设计的主要硬件平台,其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。

在修改和升级时,不需额外地改变PCB电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件开发工作,缩短了系统设计的周期,提高了实现的灵活性并降低了成本。

ASIC(Application Specific Integrated Circuit),即专用集成电路,是一种为专门目的而设计的集成电路。是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC分为全定制和半定制,其亮点在于专用,量身定制所以执行速度较快。一句话总结就是,市场上买不到的芯片。

哪个前景更好?

FPGA工程师的岗位需求主要分为两种,一是做产品设计,在fpga上直接做设计开发。最终的目的是将fpga设计相关产品推向市场。

二是做专门做fpga原型验证,就是针对ASIC设计中的功能先在FPGA上进行功能验证,保证ASIC开发功能正常,这种主要是测试使用,设计不会当最终的产品被推广,因为最终的产品是ASIC芯片。

ASIC工程师从前端设计,验证,综合,DFT到后端,每个流程岗位都有对应的职责需求,每个岗位所需的技能与知识储备也不尽相同,需要各个环节相互合作配合才能保证设计的正确性,任何一个环节出错,都可能到导致整个项目的失败。

所以ASIC设计所需的人才需要具备谨慎,耐心这些特质,只有能考虑到各个方面会出现的错误才能保证流程的正确性。

虽说目前FPGA工程师发展前景确实不错,但是相对于ASIC设计工程师还是有一定的差距的,首先FPGA工程师市场需求没有ASIC设计工程师那么大,FPGA工程师市场上并不稀缺,甚至有不少人在上大学的时候几千块买一块FPGA板就可以自己开发。

从岗位需求上来看,ASIC工程师人才需求更大,相关的技能要求也比较高,所以薪资待遇也比较高。但具体选择哪个,还是得看个人需求。总体来说,ASIC的发展前景会更好。

刚入行IC的话,如果相关技术能力不够的话,你也可以从FPGA开发做起,等积累相关经验之后就可以转到ASIC岗位。

FPGA方向的数字IC 设计赛道怎么样?来听听工程师的见解

这个职位说白了 FPGA 有两个用途,一个叫particle,part type叫原型验证。这是什么意思?我今天要做一个芯片,打个比方,要跑一场马拉松,但是我现在可能没有马拉松的场地我可能先找个操场练练手。

当然操场可能局限比较小一点,所以FPGA 现在没办法预测到我最后芯片的一个实际情况但是没关系,我可以先把我的 design 放到 FPGA上面,放到操场上先跑一圈,看一下我的逻辑也好,我的基本的功能也好,当然这个时候肯定就跑得慢。所以看它能不能够功能上是自治的,或者是一些设计原理上是自治的。

这是第一个方向叫 part type,一个验证verification。第二个方向叫刚才讲的基于 FPGA 的数字设计,不用真正流片,我可能说我的设计可能频繁改版,像软件一样。这个时候我可能就会把我的设计在FPGA 上实现,并且我不需要跑很快。

这种情况下我就需要把我的design 放到 FPGA 上面。这种情况它的好处或前景是什么?你假定现在掌握到你们整个团队的设计流程,或者思想,你是不是可以创业? 我因为我有我的师兄,包括他们的有类似的经历当然他肯定是不会去破坏原有公司的产品,这是一个职业道德。所以我觉得基于FPGA 方向来看也还不错。特别是对于那些未来可能想创业创业,其实你也不需要很大的赛道。

像华为这种大公司,不用害怕大的竞争对手进来。但是对于你而言,比如组一个小团队,三四个人,把整个市场吃下来,你可能几个人就平分掉一千万可能的利润,这样对你们几个人还是蛮不错的,所以这个方向也不错。

我觉得如果你有创业的志向的同学,特别是在IC 方向创业的,如果是走存在的 IC 的 desin 去流片方向,耗费的资本可能会比较大,你得上亿。所以FPGA 是比较适合创业。

如果你当下对入行/转行有一定困惑和意向,或者想了解项目,以及免费获取学习资料,任何关于转行的问题都有老师会为你解答。

这里放个入口:入行指导