PCIe 5.0 基础规范 v1.0 在 2019 年年中发布以后,Synopsys 发布了世界上第一款支持 PCIe 5.0 基础规范 v1.0 的 IP,并展示了在其实验室验证发射机/接收机 Tx/Rx 性能的环境,Intel 也在 2019 年 PCI-SIG 开发者大会上发表的文章展示了基于 10 nm 工艺的 PCIe 5.0 32GT/s SerDes分析与验证的场景,在10月份,Synopsys 与 Intel 联合展示了 Synopsys 的DesignWare PCIe 5.0 IP 与 Intel 下一代 XEON 处理器的进行完整的系统互操作实验。

今年虽然遭遇了疫情,但PCI-SIG依然有条不紊的制定 PCIe 5.0 CEM 规范和测试规范,PCI-SIG 下属工作组包括 CEM 工作组 和 SEG 工作组展开了非常多的线上技术讨论,并组织了虚拟的 workshop 和开发者大会。陆续更新了 PCIe 5.0 CEM 0.7/0.9 版本规范,在今年 10月,更新了 PCIe 5.0 PHY Test Spec 0. 5版本。这些版本的发布,意味着 PCIe 5.0 系统规范和测试规范已经进入到最后完善及步入验证实施的阶段。

图1 PCIE 5.0 规范进程

另外,按照去年 PCI-SIG 发布的路线图,基于两年一次规范版本升级、速率翻番的计划,2021 年协会将发布基于 PAM-4 技术的 PCIe 6.0 规范,目前协会也在开展 PCIe 6.0 基础规范的开发,最近协会发布了 PCIe 6.0 基础规范发布了 0.7版本,供协会会员审核与讨论。

图2 PCIE 6.0 规范箭在弦上

为了推动 PCIe 5.0 测试规范的完善、芯片与系统厂商的早期验证及验证测试仪器厂商的测试方案,PCI-SIG 计划在2021年2月底举行 PCIe 5.0 (32GT/s only) 初步的 FYI 测试活动,测试内容包括LEQ, TX/PLL, Link Transaction and Configuration 测试,也会对 PCIe 5.0 CEM测试夹具进行验证。现在协会已经发出邀请接受相关报名。

本文主要的目的是梳理目前 PCIe 5.0 的关键技术的进展脉络和测试方法思路。因为PCIe 5.0测试规范还没有定稿,有些内容在协会还处于讨论阶段,未来还会继续优化和改进,请大家关注 PCI-SIG后续的会议及其发布的文件规范。作为 PCI-SIG 董事会成员中唯一测试测量方案供应商,我们也欢迎行业内各位专家与 Keysight 进一步深入交流与合作。

PCIe 5.0 CEM 规范和测试规范的更新

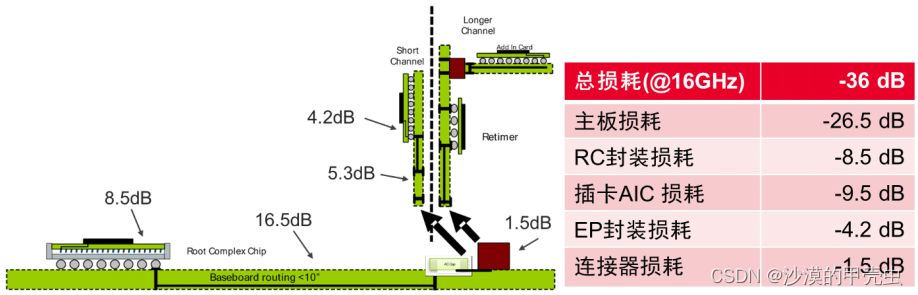

链路损耗总体规划和分配

包括 CPU 和 AIC 芯片封装在内的端到端总链路损耗 - 36dB @ 16GHz,对于由两个连接器如通过Riser卡转接的方式需要考虑总体损耗裕量,通常要在链路中加入Re-timer芯片。在最近的规范中明确了插卡 AIC 总的损耗,不论是发射路径或者接收路径,包括从金手指边缘经过 PCB,过孔,隔值电容,芯片封装等,总损耗不能超过 -9.5 dB @16GHz。PCIe 5.0金手指插槽采用SMT的插座,损耗不能超过 -1.5 dB@16GHz。另外CPU封装典型损耗 -8.5dB,AIC 芯片封装损耗 -4.2 dB。理解 PCIe 5.0 的链路损耗,对于发射机/接收机 Tx/Rx 测试所需要搭建的拓扑结构就会有更清楚的认识。

图3 PCIE 5.0 CEM规范定义的链路裕量分配

发射机 Tx 测试的指标要求与测试方法

1. PCIe 5.0的CEM中定义了系统主板和 AIC卡的发射机 Tx 眼图指标如下:

图4 PCIE5.0 CEM规范发射机 TX 端眼图指标

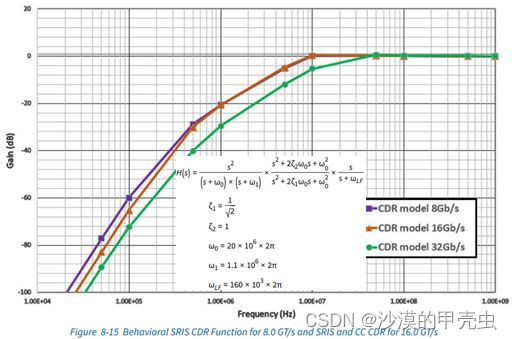

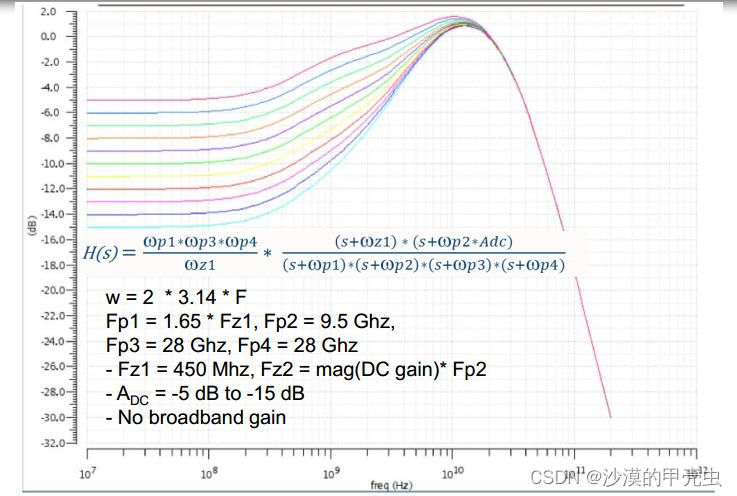

发射机 Tx 测试是基于上述的系统链路分配的组网环境下完成的,包括测试通道以及对端芯片封装模型,具体测试组网将在下面的第3点详细说明。另外,在做眼图的信号参数计算时,需要经过PCIe 5.0基础规范里定义 CDR 和接收均衡器 (CTLE+DFE) 模型,如下图所示。

图5 PCIE 5.0 CDR和均衡模型

目前官方已经发布了初步的 PCIe 5.0软件工具 Sigtest Phoenix 5.0.10 Beta版本,支持基础规范和 CEM 规范的大部分校准和测试场景,相信后续还会逐步完善。

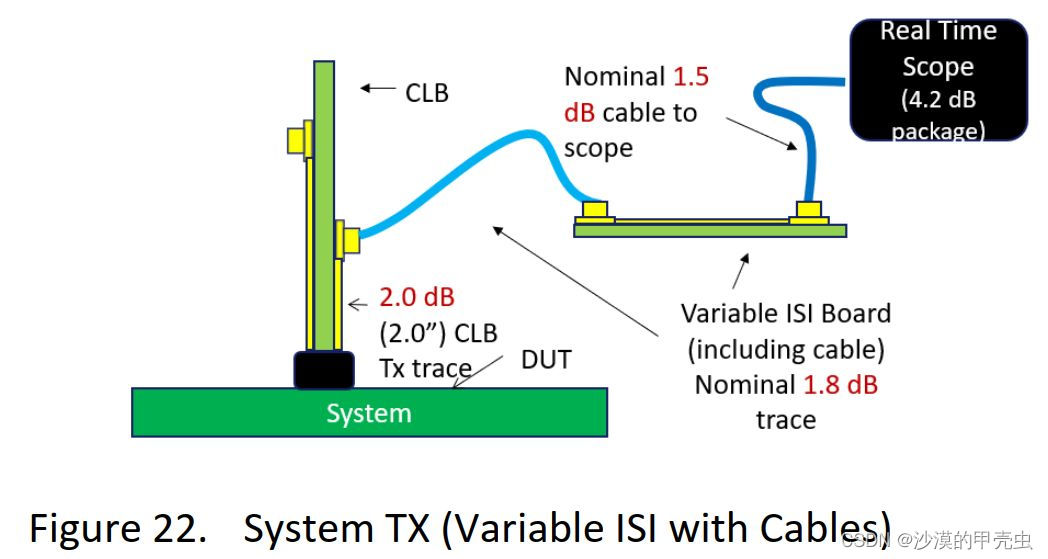

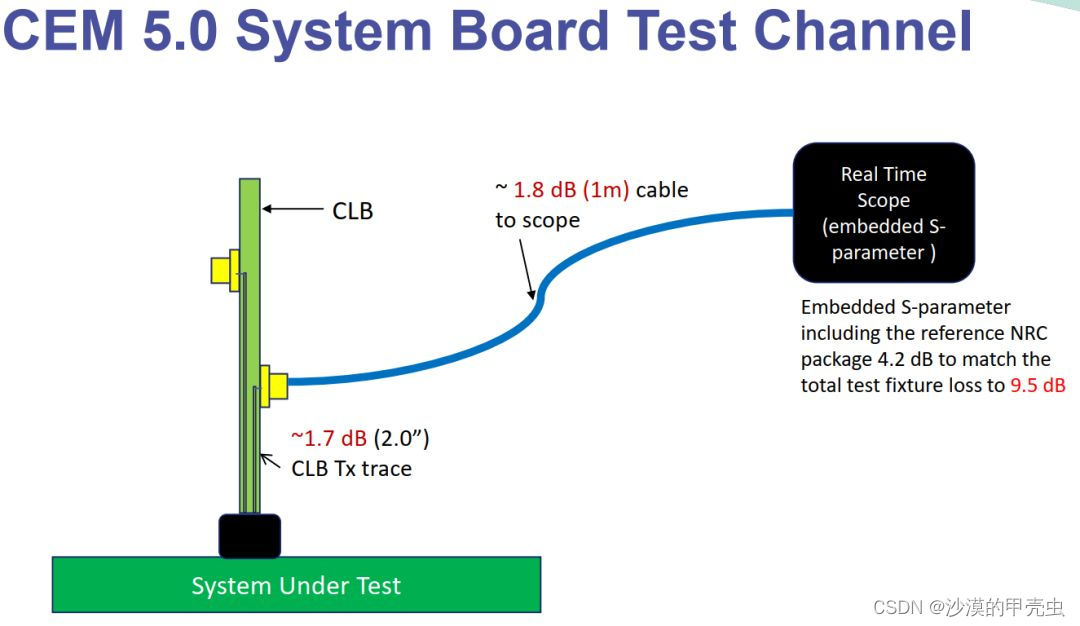

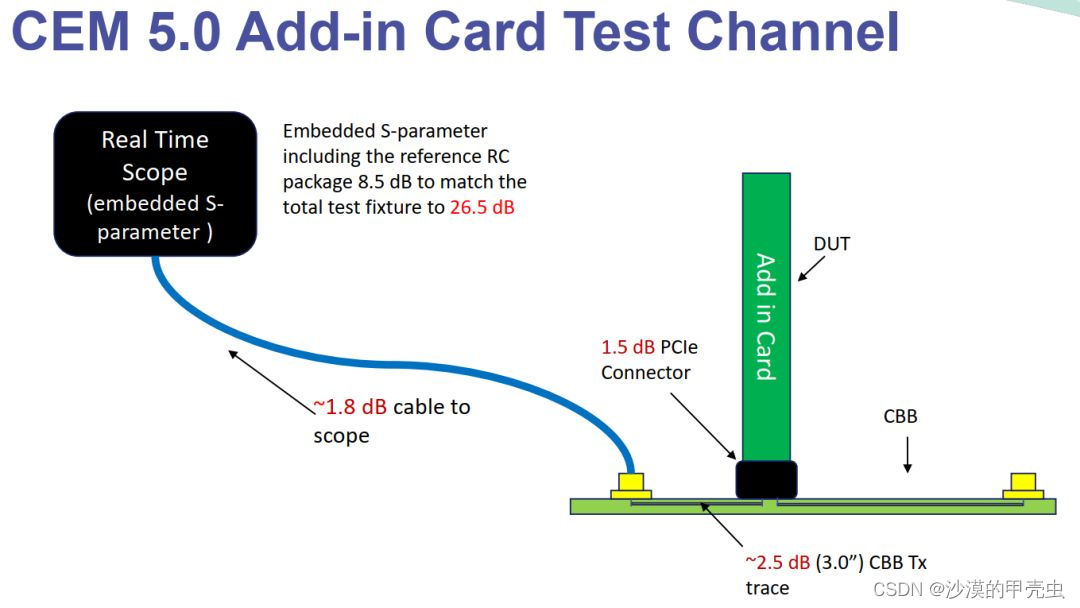

2. 对系统主板的测试,PCIe 5.0 32 GT/s不再使用Dual Port 测试方法,也就是说,测试发射机 Tx 时只需要将测试Data Lane的差分信号接到示波器,不需要同时捕获差分时钟信号。但有一点需要明确的是,在 16 GT/s 及以下速率依旧采用 Dual Port 测试方式,对于 16 GT/s的测试采用同轴电缆连接的方式,仍然需要4通道同时打开时示波器维持 25 GHz 带宽。下图展示了PCIe 5.0 32GT/s系统主板和 AIC 的测试组网方法。

图6 PCIE5.0 CEM 发射机 TX 测试示意图

3. 自 PCIe 4.0 开始,CEM 夹具里引入了可变ISI板夹具,这个夹具上设计了以接近 0.5 dB 损耗步进的若干差分走线对,在发射机/接收机 Tx/Rx 测试之前,需要使用 网络分析仪 VNA 标定和选取合适的走线对,构建规范要求的总链路损耗目标。如上图所示Tx测试时级联经过标定的ISI走线对,以及示波器嵌入对端芯片封装损耗。

有一点变化的是,对于PCIe 5.0 发射机 Tx 测试,协会会也在考虑使用 S 参数嵌入的方式,取代可变 ISI 板,将上述的 发射机 Tx 测试组网简化为下面的测试组网图,在示波器内嵌入除了夹具和测试电缆外的链路损耗 S 参数:

图7 采用软件嵌入 S 参数方法简化的 CEM 发射机 TX 测试组网图

在 PCIe 5.0 PHY Test Spec v0.5中,对发射机 Tx 测试已经按这种嵌入 S 参数的方式要求,但这种方式与硬件ISI夹具连接的方式对测量结果的一致性如何?PCI-SIG协会计划在我前面提到的明年PCIe 5.0初步workshop中进行验证和比对。需要注意,用 S 参数取代走线的方法这只适用于发射机 Tx 测试,接收机 Rx 测试仍然需要使用实际的可变 ISI 夹具板。

4. 在 PCIe 4.0 之前规范采用 Dual Port 的测试方法,基于系统主板的Common Clock架构,对系统发射端包括参考时钟在内的特性进行评估,但PCIe 5.0取消了Dual Port的测试方法,只测试发射机 Tx 信号链路特性,这对于提供参考时钟架构下的主板和 AIC 互操作可能存在一定风险,所以从 PCIe 5.0 开始,对系统主板的参考时钟有专门的测试要求,我们会在参考时钟章节进行进一步阐述。

PCIe 5.0 CEM 测试夹具更新

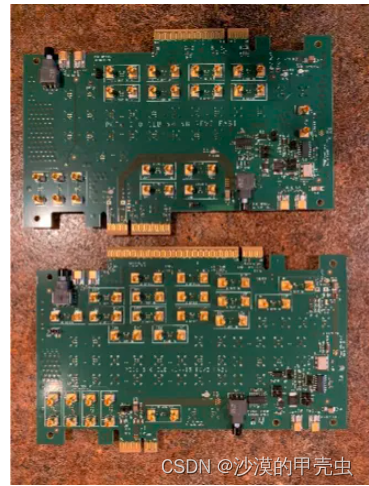

下图是 PCIe 5.0 CEM 测试夹具的实物图,CEM 夹具和 Base Spec 夹具一样适用了 MMPX同轴接头,采用低损耗板材,目前 CEM 夹具处于小批量状态,在明年初的 workshop上,将会和仪器厂商进行相关性的验证。

图8 PCIE 5.0 夹具

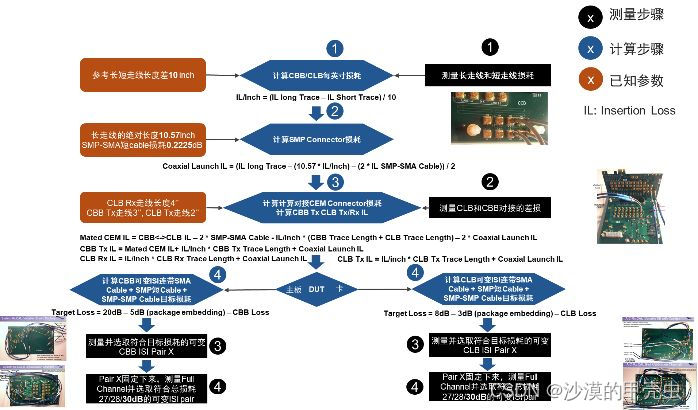

夹具套件中包含了 CBB,CLB 和可变 ISI 板,及若干 MMPX 短线。需要使用频率范围至少 20 GHz 的 VNA,测量在 PCIe 5.0 32GT/s的奈奎斯特频率点 16 GHz 下,电缆、夹具 PCB、接头、CEM插槽等损耗,选取Tx和Rx测试目标损耗所需要的ISI走线对,总体测量和标定方法与PCIe 4.0类似,如下所示,用 Keysight PNA-X系列 VNA 测量完整通道组网损耗的测试实物图,及标定夹具流程图。

图9 PCIE4.0/5.0完整测试组网链路损耗验证示意和流程图

https://www.keysight.com/zh-CN/pcx-x205186/pna-network-analyzers-300-khz-to-11-thz?nid=-32497.0.00&cc=CN&lc=chiwww.keysight.com/zh-CN/pcx-x205186/pna-network-analyzers-300-khz-to-11-thz?nid=-32497.0.00&cc=CN&lc=chi正在上传…重新上传取消

PNA 网络分析仪,900 Hz 至 120 GHzwww.keysight.com/zh-CN/pcx-x205186/pna-network-analyzers-300-khz-to-11-thz?nid=-32497.0.00&cc=CN&lc=chi正在上传…重新上传取消

PNA/PNA-X 毫米波网络分析仪――10 MHz 至 110 GHz,可扩展至 1.05 THzwww.keysight.com/zh-CN/pc-1459745/millimeter-wave-network-analyzer-systems?nid=-32259.0.00&cc=CN&lc=chi正在上传…重新上传取消

PCIe 5.0 CEM Tx测试的几个问题

CEM Tx测试带宽和采样率的要求

在 PCIe 5.0 PHY Test Spec中,对于 AIC 或者系统主板Tx 信号质量一致性测试,要求示波器的带宽设置为 33 GHz,采样率至少达到 128 GSa/s,如果示波器硬件采样率达不到这个要求,允许使用Sin(x)/x内插,但至多允许加入一个内插点,也就是最多是原始采样率的两倍,保证每个UI至少有4个采样点。

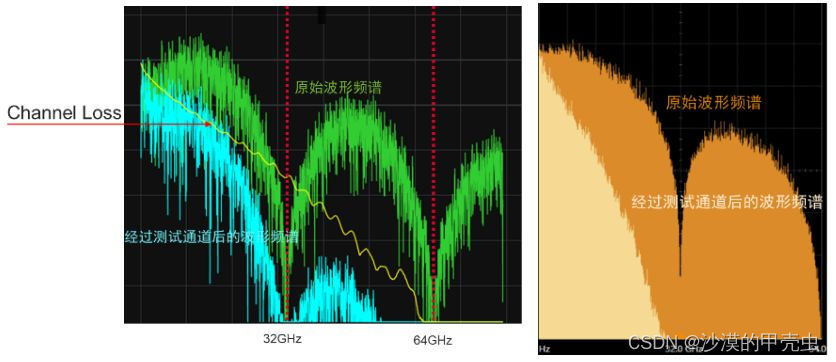

关于 CEM Tx 测试带宽问题的理解,由于在系统级的测试,考虑到CEM端到端的链路损耗达到 -36 dB@16GHz,原始信号(下图绿色频域谱线)经过传输测试通道的低通特性后,信号中的高频成分被相当程度的抑制( -36dB @ 16 GHz),由于示波器本身的动态范围的限制,高频成分会淹没在仪器本身的噪声中,对信号均衡和重建来说,低信噪比的高频成分并不会提升信号本身的计算精度,协会要求的 33 GHz带宽是一个合理的选择。但从另外一个角度来看,提升示波器的 ADC 分辨率并降低仪器本底噪声是提升测量精度的不二选择。

图10 PCIE5.0 CEM TX测试带宽

还需要注意两点:

1. 上述要求针对的是Tx的信号质量测试的示波器带宽选择,对于Tx Link EQ与上述的要求一致,同样是 33 GHz 带宽,128 GSa/s采样率。但有一点需要注意,Tx Link EQ的测试组网中,BERT误码仪输出的差分信号,以及DUT环回的差分信号,分别通过同轴分路连接的方式连接到示波器的 4 路通道,进行激励响应测试,也就是说示波器在4通道同时工作时要满足33GHz带宽要求。

2. PCIe 5.0 测试在做Rx校准时,示波器带宽至少需要 50 GHz。

图11 PCIE5.0 TX LinkEQ 测试组网示意图

另外补充一点:PHY Test Spec定义的是对系统级别的测试要求,对于 PCIe 5.0 的芯片测试,要遵循 PCIe 5.0 Base Spec,要求的示波器带宽 50 GHz。

测量精度的影响因素

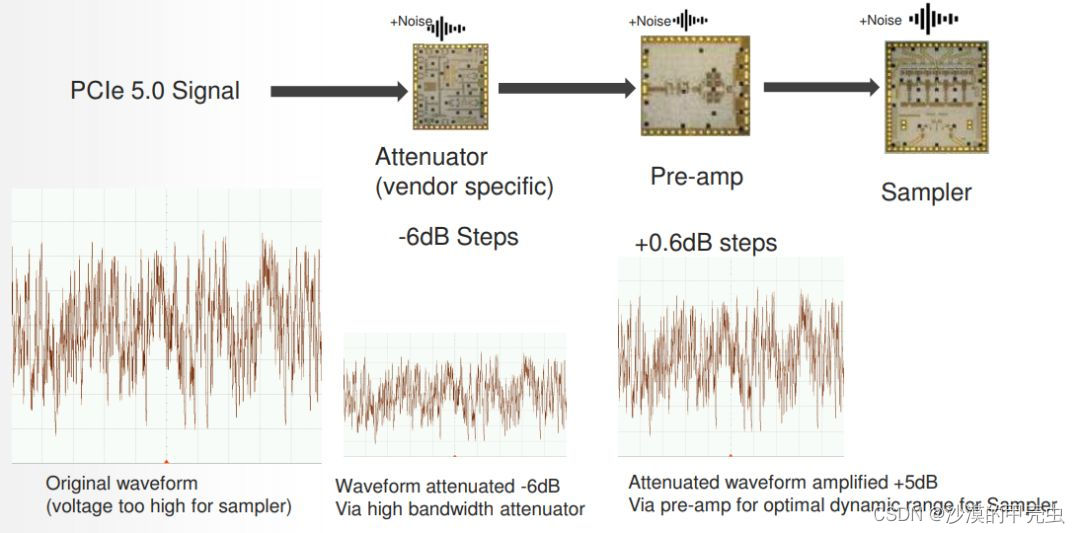

前面讲到,由于信号经过链路衰减,以及示波器本身的动态范围的影响,在Tx测试时规范要求了折衷的33GHz。在这种测量链路环境下,测试仪器本身和测试方法对测量结果的影响是不可忽略的,下面我们来分析一下,哪些因素会影响到信号的测量精度。示波器内的信号采集链如下图所示:

图12 示波器前端信号采集链路

信号进入示波器后,经过模拟前端包括衰减器、放大器、采样器,再进入到 ADC,示波器中所使用的半导体工艺、封装设计、互连设计,ADC 的垂直有效位数等的差异,会导致信噪比会存在差距。所以,降低仪器底噪、提升 ADC 的位数会为提升测量精度带来非常大的帮助,在足够采样率的条件下,这些性能超过了采用更高采样率对测量结果的影响。

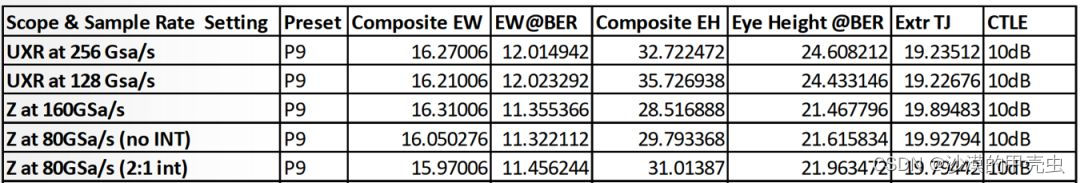

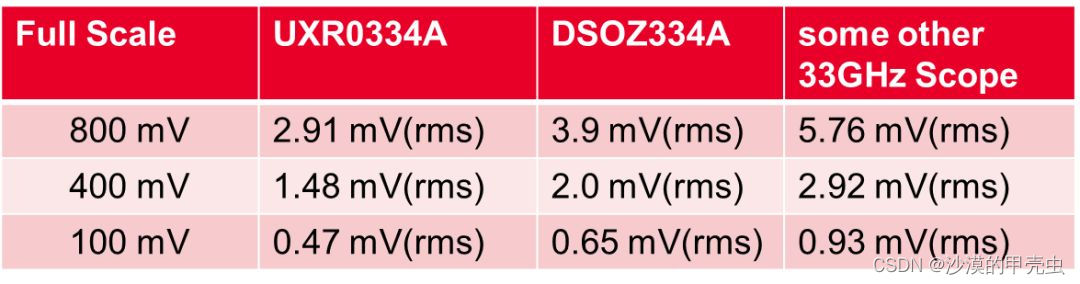

另外从测量方法上来说,垂直刻度的设定会影响到测量的信噪比,测量时有一点比较重要的是,要优化垂直刻度,让信号尽量充满垂直满量程,这样会达到最佳的测量信噪比。在Keysight 提交给协会的测试数据也验证了这样的观点,从下表中可以看到,在相同的测试条件下:使用 M8040A误码仪,加入一定的压力,经过 PCIe 5.0 Base夹具构建的36dB的损耗,设置相同的 Preset P9,使用相同的接收 CTLE DC Gain 10dB,示波器都优化调整了垂直刻度。

基于 InP HB2C 工艺 MMIC 前端、多芯片三维封装互连和 10bit ADC UXR系列示波器在 PCIe 5.0 的基于 1e-12 条件下的眼高、眼宽、TJ 等结果有明显更高的裕量。

表1 不同采样率测试结果对比

以33GHz带宽的UXR示波器为例,在相同垂直满量程的条件下,UXR的底噪指标是同行33GHz带宽示波器的一半水平。

图13 不同型号示波器底噪对比

PCIe 5.0 参考时钟抖动测试

如前文所述,PCIe 5.0 取消了系统主板 Dual Port 测试模式,但专门定义了参考时钟的测试内容。

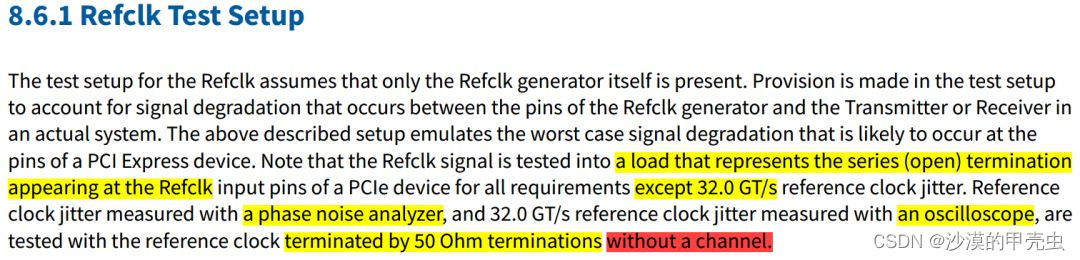

PCIe 4.0 及之前的规范,参考时钟的抖动要求只在基础规范里有所体现,我们先来回顾一下在基础规范中对参考时钟抖动的要求,基于共同时钟架构中 Tx/Rx PLL 及 CDR 的传递函数组合下,32 GT/s的参考时钟抖动小于或等于150 fs RMS,考虑到系统互连引入的噪声,这个指标放宽到 250 fs RMS,但测试组网不同以往,32GT/s的参考时钟需要通过50ohm端接的方式直接测量,也取消了之前定义的参考通道,这样做主要是为了提升信噪比提高测量精度。

图14 Base Spec PCIe 5.0 REF CLK测试说明

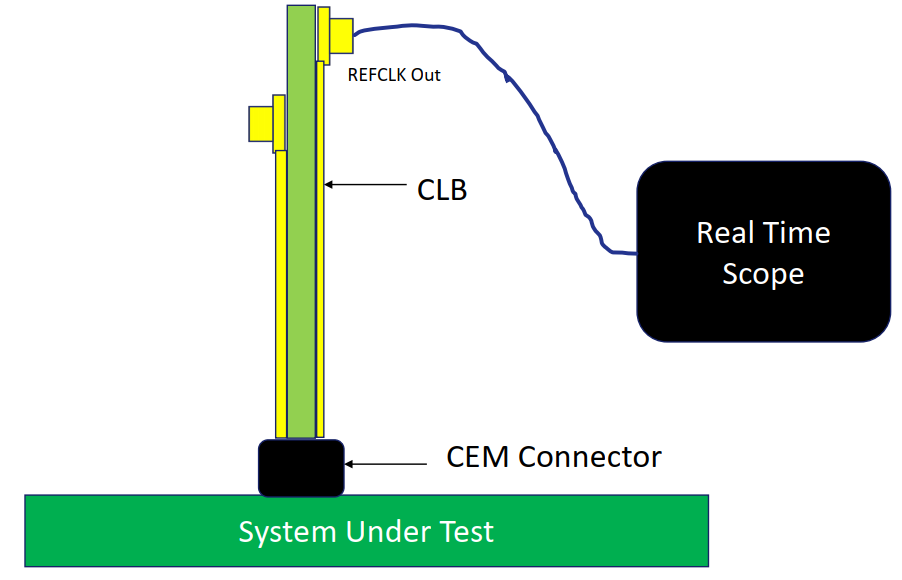

在系统级的 PCIe 5.0 PHY Test Spec v0.5 版本已经列入了参考时钟抖动的测试内容,将 CLB边缘 SMP 接口的时钟信号直接通过同轴电缆接入示波器,示波器带宽至少 5 GHz,这部分内容大家可以关注后续更新,目前抖动参数的范围和抖动测试工具还处于 TBD 的状态。

越来越高的参考时钟抖动要求对测量工具的触发抖动和本底抖动即通道间的固有抖动(差分测量需考虑通道间固有抖动)等指标都提出了越来越高的要求和挑战。

10 月底,Intel 提交了参考时钟初步建议,其中Rj的数值建议为 200 fs,从测试的角度来看,由于规范要求的指标范围非常苛刻,虽然测试算法中会加入多组传递函数滤波器,但仪器自身的固有抖动如果太大,可能还是会对测量结果的裕度造成影响。在最近一次的 PCI-SIG SEG工作组的会议中讨论了相关的内容,后续会有进一步更新,包括 Clock Jitter Tool,大家可以关注规范后续的进展。

图15 REF CLK测试示意图

另外, Intel 已经向其 OEM/ODM 发布了 Intel Clock Jitter Analysis Tool可以进行 PCIe 5.0 参考时钟抖动测试,其中有一些很有特色的功能比如示波器底噪去嵌,Midbus探测,自动带宽限制等功能。Keysight 示波器内的 D9050PCIC 一致性测试工具也包含了 PCIe 参考时钟抖动分析工具,Keysight 示波器内的相噪分析选件 D9020JITA 使用了相噪分析仪E5052B 的经典互相关算法,基于UXR系列示波器可以进行精确的参考时钟相噪测量。

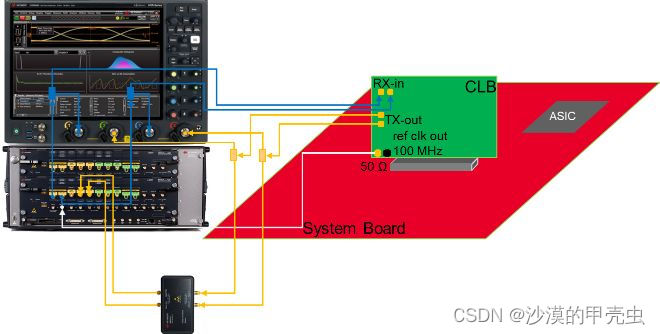

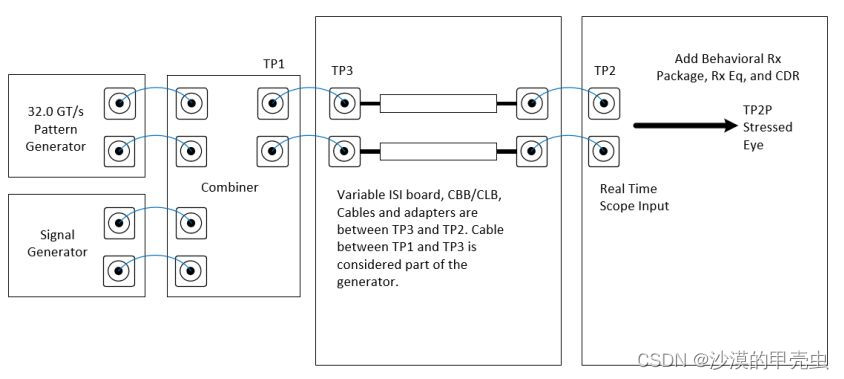

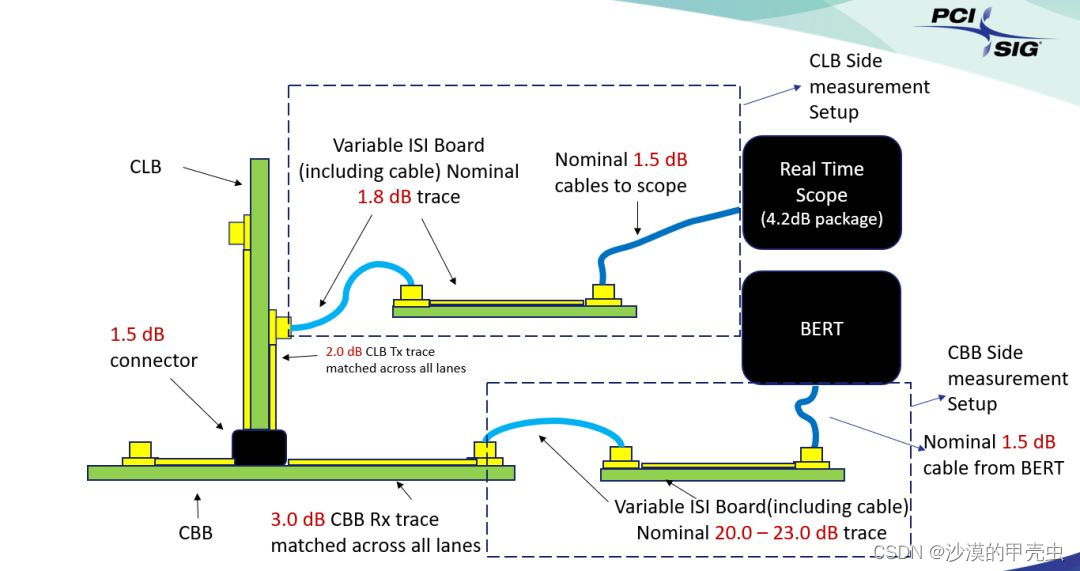

PCIe 5.0 Rx测试

首先我们先来看一下 5.0 的校准:校准分为两个测试点,如下图所示,分别是在TP3点也就是BERT输出经过电缆连接到示波器,分别校准信号幅度800mV/720mV,TxEQ,Rj,Sj,第二个部分是从TP3继续延伸经过可变ISI板及CBB和CLB后的TP2点,示波器内嵌入芯片封装S参数,以及经过参考CDR和均衡器后TP2P的压力眼图校准,TP2P校准的目标值分别为EH 15+/-1.5mV, EW 9.375+/-0.5ps。

图16 PCIE 5.0 RX 测试校准点示意图

需要注意的是 32 GT/s 的 Rx 校准要求示波器带宽设置为 50 GHz,采样率大于或等于128 GSa/s,并且由于TP3点的校准电压为差分 800 mV,50 GHz带宽示波器通道的输入电压要满足这个幅度测量量程,如果加入外部衰减器,因为 TP2P点校准要经过最大 loss 达到 37 dB 的损耗,在加入外部衰减器的情况下,信噪比再度恶化会造成校准精度的恶化。

完整的通道选取校准要从最大的包括封装损耗的 -37 dB 开始 ( PCIe 4.0 PHY Test Spec v1.01 标准也要求从最大 -30dB开始),搜寻 Preset 和 CTLE 组合,找到最大的EH*EW 眼面积,然后扫描 Sj 和 DMI,以及可以调整Vswing,计算EH和EW是否落在EH 15+/-1.5mV, EW 9.375+/-0.5ps范围,如果不满足,就步进减小ISI pair,重复上述过程,注意每一步都要扫描Preset 和 CTLE 组合,直到找到这个 ISI pair,最小可用的ISI 损耗是 -34dB。下图是系统主板和AIC的完整通道校准组网。如果不能完全遵守规范的要求,可能导致加压SJ/DMSI等达不到规范的要求,就无法真实反映 DUT 的 Rx 性能。

图17 PCIE5.0 RX 测试校准组网图

下图是系统主板Rx LEQ测试组网图

图18 SYS Board RX LEQ测试组网图

Rx LEQ测试是评价被测件Rx对压力信号的容忍性能,反映的是Rx端对抖动跟踪能力和对恶化信号的均衡能力,以误码率来评价。

测试要尽量避免在环回路径引入误码,由于服务器主板 32 GT/s环回信号损耗较大,在环回测试时,信号经过CLB直接接入BERT ED,不加额外ISI板,可以训练DUT目标TxEQ值,使环回信号Tx质量调优,SEG工作组也有讨论允许在信号环回接到BERT的路径上加入外部repeater,PCIe 5.0 Rx 测试的 BERT M8040A 的ED自带内部均衡器,也可以级联外部均衡器 M8047A,避免由于环回信号衰减引入的额外误码。下面的实验场景模拟了在环回路径损耗包括电缆损耗超过30dB的环回通道下,M8040A 误码仪接收测试做到0误码。

图19 M8040A RX LEQ环回验证实测+

小结

最后做一个总结,下图是Keysight 针对 PCIe 5.0/6.0 的完整测试方案,Keysight 是唯一一家完整提供从建模、仿真、互连参数表征、Tx、PLL 和 Rx 测试解决方案的公司。

明年即将发布的 PCIe 6.0 标准将采用 PAM-4 技术,现有的方案硬件已经就绪,PAM-4 信号天然的信噪比要比 NRZ 信号恶化 9.6 dB,它对噪声更加敏感,对测量仪器来说,如前所述基于 10bit ADC 的和拥有业内最低底噪水平的UXR 示波器能更好的应对这种挑战;M8040A误码仪的码型发生器 PG 和误码检测器 ED 硬件支持 NRZ 和 PAM-4,支持 PCIe 5.0 的链路协商,无需更换硬件或多种硬件模块冗余。