GEM TSU Interface Details and IEEE 1588 Support

- Chapter 1: Introduction

- Chapter 2: GEM TSU Clock Source

- PCW 中的 GEM TSU 时钟源选择

- 使用 PS 内部 IOPLL 作为 GEM TSU 时钟

- 使用 MIO 时钟作为 GEM TSU 时钟

- 使用 EMIO 时钟作为 GEM TSU 时钟

- GEM TSU 时钟框图

- 内部 IOPLL 作为 TSU 时钟源寄存器配置

- MIO50/51 作为 TSU 时钟源寄存器配置

- EMIO 作为 TSU 时钟源寄存器配置

- Chapter 3: TSU and PTP signals

-

- Chapter 4: Testing PTP on board

- Setup

- Master Setup

- Slave Setup

- Steps for testing PTP

- Expected PTP drift log

- Chapter 5: Accuracy for GEM PTP support on Zynq UltraScale+

- Additional Information

Chapter 1: Introduction

GEM 中的 1588 时间戳单元 (TSU) 是一个定时器,实现为 102 位寄存器。 高 48 位计算秒,接下来的 30 低位计算纳秒,最低 24 位计算亚纳秒。 当计数到一秒时,低 54 位翻转。

GEM0 的外部 TSU 端口向顶层用户公开。 外部端口为 94 位宽,符合上述定义的内部 TSU 计数的最高有效位。

Chapter 2: GEM TSU Clock Source

使用 GEM 时,目前您可以为 TSU 时钟选择 3 种不同的时钟源。

以下部分讨论如何在 PCW 配置中进行选择。

PCW 中的 GEM TSU 时钟源选择

使用 PS 内部 IOPLL 作为 GEM TSU 时钟

当您启用 GEM(例如 GEM0 )但未选择 GEM TSU 时钟时,它将默认使用 250MHz PS 内部 IOPLL 作为 GEM TSU 时钟。

Figure 1: Enable GEM0

Figure 2: GEM_TSU Clock to PS IOPLL

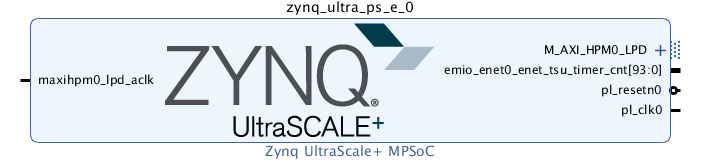

使用 GEM0 时,emio_enet0_enet_tsu_timer_cnt[93:0] 端口将暴露给用户。 由于 MIO 引脚数限制,此端口仅适用于 GEM0。 此端口是 TSU 定时器计数值。 高 48 位是秒值,低 46 位是纳秒/亚纳秒。 第 46 位每秒切换一次,即 1 pps。

Figure 3: External TSU Timer Port Available

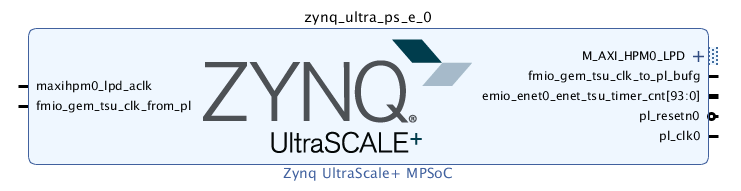

fmio_gem0_tsu_clk_to_pl_bufg 和 fmio_gem_tsu_clk_from_pl 信号也应该暴露在顶层,因为 fmio_gem0_tsu_clk_to_pl_bufg 是 94 位定时器正在同步的时钟。

在 2018.2 PCW 中,此配置隐藏了这对信号。 计划在未来的版本中修复此问题。

使用 MIO 时钟作为 GEM TSU 时钟

要将 MIO 50 或 51 用作 TSU 时钟,用户需要启用“GEM TSU 时钟”并在 PCW GUI 中启用 MIO。

Figure 4: Choose MIO 50 as TSU Clock Source

Figure 5: GEM_TSU Clock to MIO 50

Figure 5: GEM_TSU Clock to MIO 50

Figure 6: TSU loopback Clock Ports Available

这两个端口(fmio_gem_tsu_clk_to_pl_bufg 和 fmio_gem_tsu_clk_from_pl)可以以环回方式连接。 94 位 TSU 定时器端口 emio_enet0_enet_tsu_timer_cnt 与 fmio_gem0_tsu_clk_to_pl_bufg 时钟同步,定时器数据的本地处理取决于该时钟。

请注意,MIO_26 不应用于任何 GEM 信号。 这将在未来版本的 PCW GUI 中“修复”。

使用 EMIO 时钟作为 GEM TSU 时钟

要将 EMIO 用于 TSU 时钟,用户需要启用“GEM TSU 时钟”并在 PCW GUI 中选择 EMIO。

Figure 7: GEM TSU Clock to EMIO

另一个额外的端口 emio_enet_tsu_clk 将暴露给用户。

Figure 8: EMIO TSU Clock Port Available

Figure 8: EMIO TSU Clock Port Available

我们通过从 ZCU102 板获取 Si570 sysclk (300Mhz) 输入并将其连接到 MMCM 来验证 EMIO 作为时钟源。 PL 中的 MMCM 生成一个 250Mhz 时钟,该时钟连接到 Vivado IP 集成器设计中名为“emio_enet_tsu_clk”的 EMIO TSU CLOCK。

GEM TSU 时钟框图

下面是 GEM TSU 时钟结构的框图:

Figure 9: GEM TSU Clock Structure

左侧的 3 个时钟是 TSU 时钟源,具体取决于在 PCW 配置中选择的内容。

Gem_tsu_ref_clk:PS 内部 IOPLL

fmio_gem_tsu_clk: EMIO

pad_gem_tsu_clk: MIO

两条红色突出显示的路径是 fmio_gem0_tsu_clk_to_pl_bufg 和 fmio_gem_tsu_clk_from_pl。

MUX 将决定使用哪个 TSU 时钟。

根据设计要求在 PCW 中配置 TSU 时钟时,相关寄存器将在 psu_init.tcl 中自动设置。

内部 IOPLL 作为 TSU 时钟源寄存器配置

GEM_CLK_CTRL -

- bit[22] = 1’b0 或 1b’1(查看 fmio 信号是否被环回)

- bit [21:20] = 2b’00

GEM_TSU_REF_CTRL –

- bit[2:0] = 3b’000 或 3b’010(根据时钟选择设置除数)

- bit [24] = 1

上面的配置已经测试过了。

您还可以简单地将 tsu_timer_cnt 中我们需要的位从探测(1PPS 的位 45 和 46)暴露到输出标头。 即,tsu_timer_cnt[93:0] → 第 45 位的反转是 1PPS 信号。

寄存器设置同上,通常 fmio_gem_tsu_clk_to_pl_bufg 和 fmio_gem_tsu_clk_from_pl 会被环回。

MIO50/51 作为 TSU 时钟源寄存器配置

GEM_CLK_CTRL –

- bit[22] = 1b’0 或 1b’1(查看 fmio 信号是否被环回)

- 位 [21:20] = 2b’11

GEM_TSU_REF_CTRL –

- bit[2:0] =3b’000 或 3’b010

- bit[24] = 1b’0

MIO_PIN_XX

- MIO_PIN_50/51 bit[1] = 1 as per user selection

由于没有可用的硬件,上述配置尚未经过测试。

EMIO 作为 TSU 时钟源寄存器配置

GEM_CLK_CTRL -

- bit[22] = 1b’1(fmio_gem_tsu_clk_to_pl_bufg 和 fmio_gem_tsu_clk_from_pl 应该始终被环回)

- bit [21:20] = 2b’11

GEM_TSU_REF_CTRL –

在这种情况下,不应为 GEM TSU 时钟配置 MIO_PIN_50/51,即,0xFF1800C8 设置为 0x00000010,寄存器 0xFF1800CC 设置为 0x00000010。 这样,时钟会自动从 EMIO 中选取。

文档 (U1087) 将在未来版本中更新 GEM_CLK_CTRL 寄存器位[21:20],如下所示:

00/10:来自 PLL 的 TSU 时钟

01:保留

11:来自 MIO[50] 或 MIO[51] 或 EMIO 的 TSU 时钟

Chapter 3: TSU and PTP signals

TSU Signals

如果用户想要控制 TSU 寄存器如何递增,他们可以在 PCW 中启用 TSU 信号并访问 emio_enet0_tsu_inc_ctrl[1:0] 和 emio_enet0_tsu_timer_cmp_val 信号。

Figure 10: Enable TSU Signals

Figure 11: TSU Ports Available

如果 gem_tsu_inc_ctrl 信号没有被强制,TSU 定时器会以四种不同的方式运行。

当 gem_tsu_inc_ctrl [1:0] =

emio_enet0_tsu_timer_cmp_val 是 TSU 定时器比较有效信号,与 TSU 时钟同步。 当 TSU 定时器计数值的高 70 位等于编程的比较值时,它被置为高电平。

PTP signals

当启用 PTP 信号时,PTP 接口也会暴露出来。

Figure 12: Enable PTP Interface

Figure13: PTP Interface Available

IEEE 1588 PTP 帧识别和时间戳单元信号:

emio_enet0_delay_req_rx:如果在接收时检测到 PTP 延迟请求帧,则断言高同步到 rx_clk。

emio_enet0_delay_req_tx:如果在发送时检测到 PTP 延迟请求帧,则断言高同步到 tx_clk。

emio_enet0_pdelay_req_rx:如果在接收时检测到 PTP 对等延迟请求帧,则断言高同步到 rx_clk。

emio_enet0_pdelay_req_tx:如果在发送时检测到 PTP 对等延迟请求帧,则断言高同步到 tx_clk。

emio_enet0_pdelay_resq_rx:如果在接收时检测到 PTP 对等延迟响应帧,则断言高同步到 rx_clk。

emio_enet0_pdelay_resq_tx:如果在发送时检测到 PTP 对等延迟响应帧,则断言高同步到 tx_clk。

emio_enet0_rx_sof:当在接收帧上检测到 SFD 时,置高同步到 rx_clk

emio_enet0_tx_sof:在发送帧上检测到 SFD 时,与 tx_clk 同步置为高电平,在帧结束时置低。

emio_enet0_sync_frame_rx:如果在接收时检测到 PTP 同步帧,则断言高同步到 rx_clk。

emio_enet0_sync_frame_tx:如果在发送时检测到 PTP 同步帧,则断言高同步到 tx_clk。

Chapter 4: Testing PTP on board

该测试通过主从同步验证 MACB Linux 驱动程序的 IEEE1588 支持。 为了在 MACB 中测试此功能,请确保打开了硬件时间戳支持选项。

例如,在较旧的内核中,需要启用 MACB_USE_HWSTAMP。 2017.4中为CONFIG_MACB_EXT_BD; 在 2018.1 中是 CONFIG_MACB_USE_HWTSTAMP。

https://github.com/Xilinx/linux-xlnx/blob/master/drivers/net/ethernet/cadence/Kconfig

这也处理了内核中的 PTP 依赖关系。 TSU 时钟是通过 DTG 从设计中获得的。 它通常为 250MHz。

Setup

当 ZynqMP 板通常是从设备时,需要进行测试设置。 主机通常是具有稳定高精度时钟的设置,用于硬件时间戳和(可选)1PPS 信号输出。

Master Setup

Oregano SYN1588 NIC 卡就是我们使用的这样一张卡。 它可以插入任何 Linux 机器的 PCIe 插槽。 此卡带有一个自定义启动映像,位于 pendrive 中。 您可以将其插入 Linux 机器并从中引导。

在这种情况下,在 Linux 机器上安装 Linux PTP 并使用相应的命令。

Slave Setup

使用任何带有以太网接口的 ZynqMP 板。 如果计划在 CRO 上捕获 1PPS 信号,则仅使用带 GEM0 的 DC4。 为了从 ZynqMP 捕获 1PPS 信号,必须更新设计以将 GEM0 时间计数器的“位 45 倒数”提取到板上的可探测接头。

Steps for testing PTP

On the Linux Host machine (Master):

ptp4l -i <interface_name> -m

On the ZynqMP (Slave):

ptp4l -i eth0 -s -m

Expected PTP drift log

e2e_slave

ptp4l -i eth0 -s -m

e2e_master

ptp4l -i -m

e2e_slave

ptp4l -i eth0 -s -m

root@Xilinx-ZC1751-DC1-2016_1:~# ptp4l -i eth0 -s -m

ptp4l[136.261]: selected /dev/ptp0 as PTP clock

ptp4l[136.262]: driver changed our HWTSTAMP options

ptp4l[136.262]: tx_type 1 not 1

ptp4l[136.262]: rx_filter 1 not 12

ptp4l[136.262]: port 1: INITIALIZING to LISTENING on INITIALIZE

ptp4l[136.262]: port 0: INITIALIZING to LISTENING on INITIALIZE

ptp4l[136.391]: port 1: new foreign master 001ec0.fffe.862d3a-1

ptp4l[140.391]: selected best master clock 001ec0.fffe.862d3a

ptp4l[140.391]: port 1: LISTENING to UNCALIBRATED on RS_SLAVE

ptp4l[142.568]: master offset -506797907644 s0 freq +0 path delay -369

ptp4l[143.568]: master offset -506797901693 s1 freq +5951 path delay -833

ptp4l[144.568]: master offset -1165 s2 freq +4786 path delay -833

ptp4l[144.568]: port 1: UNCALIBRATED to SLAVE on MASTER_CLOCK_SELECTED

ptp4l[145.568]: master offset -930 s2 freq +4671 path delay -369

ptp4l[146.568]: master offset -117 s2 freq +5205 path delay -369

ptp4l[147.568]: master offset -16 s2 freq +5271 path delay -202

ptp4l[148.568]: master offset 38 s2 freq +5320 path delay -36

ptp4l[149.568]: master offset 95 s2 freq +5389 path delay 70

ptp4l[150.568]: master offset 46 s2 freq +5368 path delay 214

ptp4l[151.568]: master offset 165 s2 freq +5501 path delay 214

ptp4l[152.568]: master offset 120 s2 freq +5506 path delay 257

ptp4l[153.568]: master offset 107 s2 freq +5529 path delay 257

ptp4l[154.568]: master offset 51 s2 freq +5505 path delay 275

ptp4l[155.568]: master offset 45 s2 freq +5514 path delay 275

ptp4l[156.568]: master offset -17 s2 freq +5465 path delay 310

ptp4l[157.568]: master offset -7 s2 freq +5470 path delay 310

ptp4l[158.568]: master offset 17 s2 freq +5492 path delay 310

ptp4l[159.568]: master offset -16 s2 freq +5464 path delay 314

ptp4l[160.568]: master offset 4 s2 freq +5480 path delay 314

ptp4l[161.568]: master offset -1 s2 freq +5476 path delay 314

ptp4l[162.568]: master offset -16 s2 freq +5460 path delay 315

ptp4l[163.568]: master offset 8 s2 freq +5480 path delay 311

ptp4l[164.568]: master offset -3 s2 freq +5471 path delay 311

ptp4l[165.568]: master offset -8 s2 freq +5465 path delay 311

ptp4l[166.568]: master offset 7 s2 freq +5478 path delay 309

ptp4l[167.568]: master offset -17 s2 freq +5456 path delay 312

ptp4l[168.568]: master offset -7 s2 freq +5461 path delay 312

ptp4l[169.568]: master offset -5 s2 freq +5461 path delay 313

ptp4l[170.569]: master offset -5 s2 freq +5459 path delay 313

ptp4l[171.569]: master offset -5 s2 freq +5458 path delay 313

ptp4l[172.569]: master offset 2 s2 freq +5463 path delay 313

DTS example

&gem0 {

tsu-clk=<250000000>;

…

};

Chapter 5: Accuracy for GEM PTP support on Zynq UltraScale+

MACB 驱动程序支持 Zynq MPSoC GEM 的 IEEE 1588。使用 Linux PTP 应用程序和我们的工程团队掌握的 Linux 服务器对主从同步进行了测试。观察到 +/- 50ns 漂移。

精度可以降低到 < +/- 10ns(7 是我们在 UNH-IOL(新罕布什尔大学互操作性实验室)的外部合规性中观察到的)。请注意,+/- 5ns 等低漂移需要进行一些调整,并且非常依赖于系统。我们并不普遍声称这种漂移是可以实现的。

为此,必须减去静态偏移——这是特定于系统的。同步后,系统的这种静态偏移可以通过在一夜之间绘制漂移来观察,例如(或在 CRO(示波器)中捕获它)并对其进行均衡以查看平均漂移。通常通过将示波器连接到主机和从机并分析它们的 1PPS 信号来捕获漂移。然后,您必须在驱动程序的 adjfreq 函数中减去/添加此参数以改善实际漂移。

Additional Information

寄存器

TSU_TIMER_INCR

- “ns_increment”和“tsu_timer_incr_sub_nsec”不与“alt_ns_incr”一起使用。

- “num_incs”将仅与 alt_ns_incr 一起使用,但我们当前的驱动程序不使用 alt_ns_incr。

NETWORK_CONTROL

GEM_CLK_CTRL

- bit [21:20] –

00/10:来自 PLL 的 TSU 时钟

01:保留

11:来自 MIO[50] 或 MIO[51] 或 EMIO 的 TSU 时钟

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)