1.1设计目的

单片机与PC机串行通信端口在系统控制的范畴中一直占据着及其重要的地位,它不仅没有因为时代的进步而遭淘汰,反而在规格上越来越完善,应用也越来越广泛。作为一种基本而又灵活方便的通信方式,串口通信被广泛应用于PC与PC或者PC与单片机之间的数据交换以及其他工业控制与自动控制中。如今,在很多场合中,要求单片机不仅能独立完成单机的控制任务,还要能与其他数据控制设备(单片机、PC机等)进行数据交换。因此如何实现PC机与单片机之间的通信具有非常重要的现实意义。

1.2设计内容

以单片机与PC机为核心,实现单片机与PC机机的串口通信。

2系统硬件电路设计

2.1系统设计框图

图2-1 系统设计框图

2.2串口通信基本原理

所谓"串行通信"是指外设和计算机间使用一根数据信号线,数据在一根数据信号线上按位进行传输,每一位数据都占据一个固定的时间长度。这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,当然,其传输速度比并行传输慢。相比之下,由于高速率的要求,处于计算机内部的CPU与串口之间的通讯仍然采用并行的通讯方式,所以串行口的本质就是实现CPU与外围数据设备的数据格式转换(或者称为串并转换器),即当数据从外围设备输入计算机时,数据格式由位 (bit)转化为字节数据;反之,当计算机发送下行数据到外围设备时,串口又将字节数据转化为位数据。

串行端口的本质功能是作为CPU和串行设备间的编码转换器。当数据从 CPU经过串行端口发送出去时,字节数据转换为串行的位。在接收数据时,串行的位被转换为字节数据。

在Windows环境(Windows NT、Win98、Windows2000)下,串口是系统资源的一部分。 应用程序要使用串口进行通信,必须在使用之前向操作系统提出资源申请要求(打开串口),通信完成后必须释放资源(关闭串口)。

串口通信的概念非常简单,串口按位(bit)发送和接收字节。尽管比按字节(byte)的并行通信慢,但是串口可以在使用一根线发送数据的同时用另一根线接收数据。它很简单并且能够实现远距离通信。比如IEEE488定义并行通行状态时,规定设备线总常不得超过20米,并且任意两个设备间的长度不得超过2米;而对于串口而言,长度可达1200米。

典型的串口用于ASCII码字符的传输。

通信使用3根线完成:(1)地线,(2)发送,(3)接收。由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。其他线用于握手,但是不是必须的。串口通信最重要的参数是波特率、数据位、停止位和奇偶校验。对于两个进行通行的端口,这些参数必须匹配:

a,波特率:这是一个衡量通信速度的参数。它表示每秒钟传送的bit的个数。例如300波特表示每秒钟发送300个bit。当我们提到时钟周期时,我们就是指波特率例如如果协议需要4800波特率,那么时钟是4800Hz。这意味着串口通信在数据线上的采样率为4800Hz。通常电话线的波特率为14400,28800和36600。波特率可以远远大于这些值,但是波特率和距离成反比。高波特率常常用于放置的很近的仪器间的通信,典型的例子就是GPIB设备的通信。

b,数据位:这是衡量通信中实际数据位的参数。当计算机发送一个信息包,实际的数据不会是8位的,标准的值是5、7和8位。如何设置取决于你想传送的信息。比如,标准的ASCII码是0~127(7位)。扩展的ASCII码是0~255(8位)。如果数据使用简单的文本(标准 ASCII码),那么每个数据包使用7位数据。每个包是指一个字节,包括开始/停止位,数据位和奇偶校验位。由于实际数据位取决于通信协议的选取,术语 “包”指任何通信的情况。

c,停止位:用于表示单个包的最后一位。典型的值为1,1.5和2位。由于数据是在传输线上定时的,并且每一个设备有其自己的时钟,很可能在通信中两台设备间出现了小小的不同步。因此停止位不仅仅是表示传输的结束,并且提供计算机校正时钟同步的机会。适用于停止位的位数越多,不同时钟同步的容忍程度越大,但是数据传输率同时也越慢。

d,奇偶校验位:在串口通信中一种简单的检错方式。有四种检错方式:偶、奇、高和低。当然没有校验位也是可以的。对于偶和奇校验的情况,串口会设置校验位(数据位后面的一位),用一个值确保传输的数据有偶个或者奇个逻辑高位。例如,如果数据是011,那么对于偶校验,校验位为0,保证逻辑高的位数是偶数个。如果是奇校验,校验位位1,这样就有3个逻辑高位。高位和低位不真正的检查数据,简单置位逻辑高或者逻辑低校验。这样使得接收设备能够知道一个位的状态,有机会判断是否有噪声干扰了通信或者是否传输和接收数据是否不同步。

2.3 AT89C51单片机简介

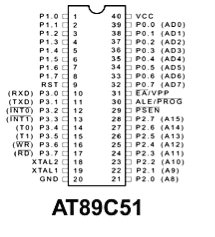

AT89C51是一种带4K字节闪烁可编程可擦除只读存储器的低电压,高性能CMOS8位微处理器,俗称单片机。该器件为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。其管脚功能如下:

VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P0口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的低八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须接上拉电阻。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为低八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。

P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 /INT0(外部中断0)

P3.3 /INT1(外部中断1)

P3.4 T0(计时器0外部输入)

P3.5 T1(计时器1外部输入)

P3.6 /WR(外部数据存储器写选通)

P3.7 /RD(外部数据存储器读选通)

图2-2 ATC89C51管脚图

2.4 9针串口

9针串口:一个完整的RS-232接口是一个25针的D型插头座,25针的连接器实际上只有9根连接线,所以就产生了一个简化的9针D型RS-232插头座,常用的就是一个9针的D型插头座。

EIA-RS-232C对电器特性、逻辑电平和各种信号线功能都作了规定:

在TxD和RxD上:逻辑1(MARK)=-3V~-15V

逻辑0(SPACE)=+3~+15V

在RTS、CTS、DSR、DTR和DCD等控制线上:

信号有效(接通,ON状态,正电压)=+3V~+15V

信号无效(断开,OFF状态,负电压)=-3V~-15V

介于-3~+3V之间的电压无意义,低于-15V或高于+15V的电压也认为无意义。因此如果要进行通信,还要对信号的电平进行转换,比如使用MAX3232芯片来转换电平。使用串口进进行通信时,我们最主要关心的时以下这三个引脚:5 GND、2 RXD、3 TXD要完成数据的发送与接收就必须要到上面这三个引脚。而其它引脚是用来控制传输规则的,即握手协议。下面是9针串口(DB9),引脚功能。引脚号缩写英文全称功能说明

1DCDData Carrier Detection数据载波检测

2RXDReceive Data接收数据

3TXDTransmit Data发送数据

4DTRData Terminal Ready数据终端准备

5GNDSystem Ground信号地

6DSRData Set Ready数据设备准备好

7RTSRequest to Send请求发送

8CTSClear to Send清除发送

9RIRing Indicator振铃指示

图2-3 9针串口引脚功能图

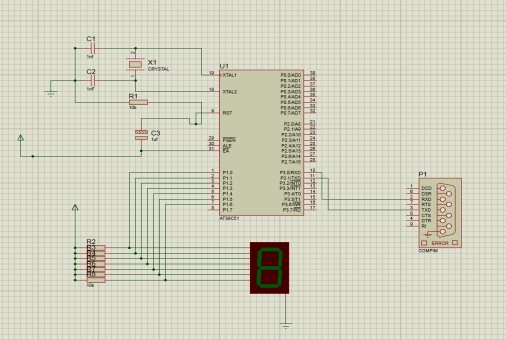

2.5硬件电路图

图2-4 硬件总电路图

3 系统软件程序设计

3.1单片机与PC总体设计流程图(见附件)

3.2主程序设计

receivedata data 40h ;存放收到的数据

displaydata data 39h ;存放显示子程序要显示的数据

ORG 0000H

JMP START

ORG 0023H

JMP COMMJUDGE

ORG 0100H

START:

MOV SP, #60H

MOV SCON, #50H

MOV PCON, #80H

MOV TMOD,#20H

MOV TL1,#0FAH

MOV TH1,#0FAH

SETB EA

SETB ES

SETB TR1

HERE: JMP HERE

COMMJUDGE:

JB TI,TT00 ;如果是发送引起的中断,那么就不管

CLR RI

CALL CHANGEDIS

CALL DISPLAY

CALL TRANS

TT00: CLR TI

RETI

3.3其他子程序设计

;********************************************************************

;=========================================

;功能描述: 串口接收数据的处理子程序

;创建日期: 2017年6月29日12:37:12

;=========================================

CHANGEDIS:

PUSH Acc

PUSH PSW

MOV A,SBUF

MOV receivedata,A

SUBB A,#30H ;数字的ASCII码转换为对应的数字(此程序仅限数字

MOV displaydata,A

POP PSW

POP Acc

RET

;=========================================

;函 数 名: TRANS

;功能描述: 串口发送数据给PC的子程序

;创建日期: 2017年6月29日12:43:48

;=========================================

TRANS:

PUSH ACC

PUSH PSW

MOV A,#2BH ;2AH是事先约定的字符,返回给PC端时,用于确认显示正确

MOV SBUF,A ;此语句产生一个TI=1.

MOV R7,#02H

DL: MOV R6,#0FFH

DL6: DJNZ R6,DL6

DJNZ R7,DL

POP PSW

POP ACC

RET

;=========================================

;函 数 名: DISPLAY

;功能描述: 显示子程序

;创建日期: 2017年6月27日22:37:46

;=========================================

DISPLAY:

MOV R1,#displaydata ;取显示缓冲区首地址

MOV A,@R1 ;查表获取段选码

MOV DPTR,#TAB

MOVC A,@A+DPTR

MOV P0,#0FEH ;对P0口进行位选,FE则最左边那位显示

MOV P1,A ;给P1口送段选码

RET

;-------------------------LED显示码表--------------------------

TAB: DB 3FH, 06H, 5BH, 4FH, 66H, 6DH

DB 7DH,7FH, 6FH,

END

4软件仿真

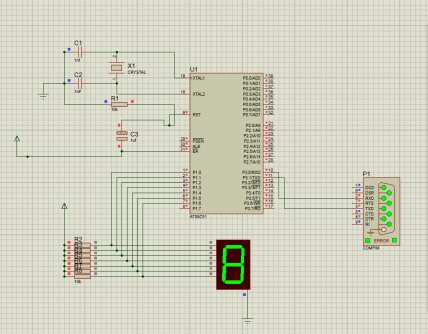

首先在protues中画出如下电路图

图4-1仿真开始电路图

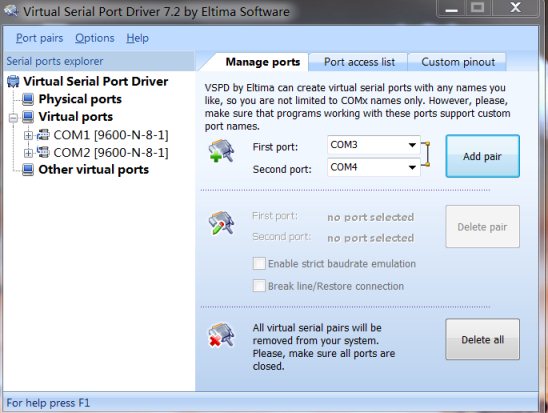

打开虚拟串口软件,建立COM1和COM2为相互连接的一对端口。

打开虚拟串口软件,建立COM1和COM2为相互连接的一对端口。

单击添加端口,即可完成端口添加。

打开虚拟串口软件,建立COM1和COM2为相互连接的一对端口。

单击添加端口,即可完成端口添加。

图4-2 建立虚拟端口

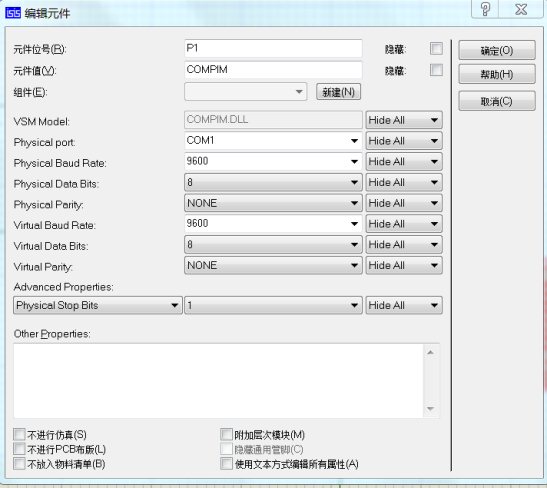

接下来对串口进行设置,设置内容如下:

图4-3 串口设置

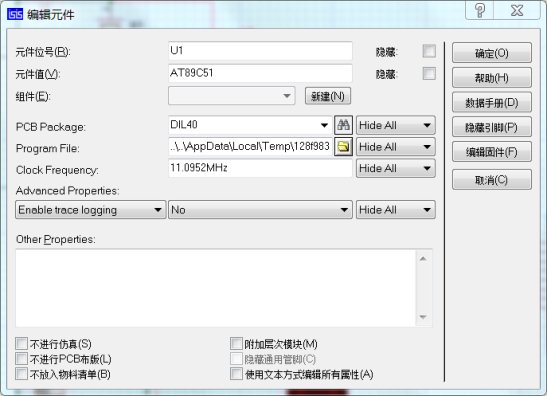

对51单片机设置

图4-4 AT89C51单片机设置

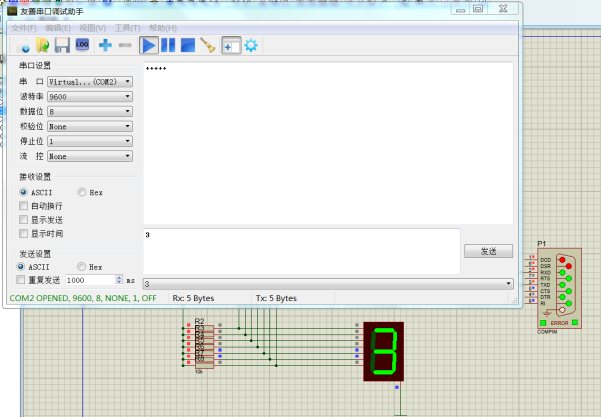

启动友善串口助手,选择COM2发送数据。向单片机发送数字3,观察单片机仿真结果。

图4-5 仿真结果

5总结

通过本次单片机间串行通信实验设计,使我对单片机有更加深刻的了解,明白了软件与硬件的配合使用,懂得怎样去分析电路及调试程序,虽然在设计过程中遇到很多困难,但是经过进一步查阅相关资料,问题才得以解决,尽管最后设计不是那么完美,不是那么理想,但总体上来说实现了单片机与PC机间串行通信,基本上完成了实验原理所需要求,通过本次设计也使得自己明白软件与硬件相结合的重要性,二者缺一不可,所以在实现硬件连接的同时也要读懂软件所实现的功能。本设计介绍了一种单片机与PC机之间串行通信的设计方法,论文首先介绍了单片机与单片机之间串行通信的工作原理、软件与硬件的实现、研究现状、串行通信的概念以及键盘输入。主要是单片机与单片机之间串行通信的方式和重要的数据位说明,接着提出了可行的设计方案,并从硬件电路设计及软件程序设计两个方面详细介绍了整个设计的工作原理及设计过程,同时验证了方案的可行性。