板卡介绍

FMC164子卡集成4通道1Gsps采样率,16位AD,4通道1.25Gsps 16位DA。板载时钟芯片HMC7044,可以提供JESD204B所需要的各种时钟。具有同步/触发功能,模拟信号采用SSMC射频连接器输入和输出。板卡可广泛应用于通信多载波,雷达与智能天线,测试与测量,软件无线电等。

板卡照片

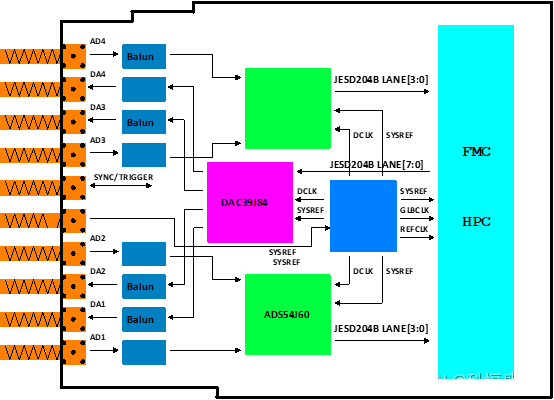

原理框图

技术指标

ADC性能指标:

☆ADC型号:ADS54J60。

☆4通道16位分辨率,1GSPS采样率。

☆噪底:-159Dbfs/HZ。

☆模拟输入带宽(3dB):1.2GHZ。

☆100dBc 通道隔离度/串扰(@170MHz)。

☆数据传输:8个LANE JESD204B。

DAC性能指标:

☆DAC型号:DAC39J84。

☆分辨率:16bits。

☆最大采样率:2.8GSPS。

☆通道数:4。

☆耦合方式:交流耦合。

☆数据传输:8个LANE JESD204B。

☆最大输入数据速率:1.25GSPS。

时钟性能指标:

☆时钟型号:HMC7044。

☆支持板载时钟/外部时钟,软件可选择

其他:

☆连接器:10个SSMC接口。

☆标准FMC子卡,符合VITA57.1规范。

☆支持外触发或内触发。

☆板卡尺寸:84.1mm X 69mm。

☆工作温度:-40℃~+85℃。