- 第一种就是使用assign语句

这种会根据代码逻辑进行综合,也会综合成三态门,但不一定是使用IOBUF这种资源。

assign a = in_or_oout ? 1'dz : out;

- 第二种就是使用原语

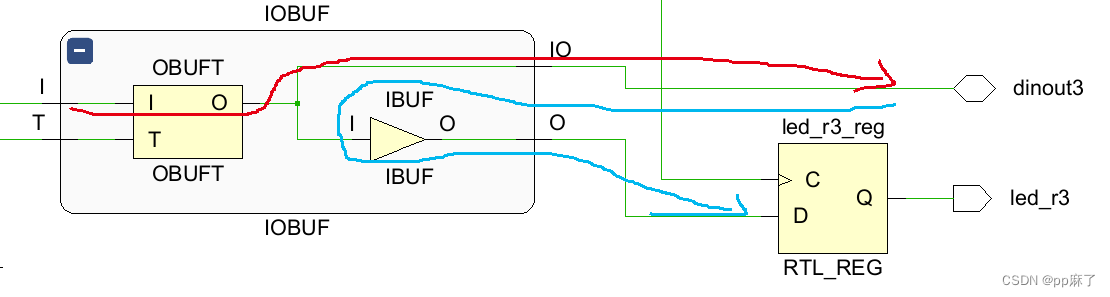

以xilinx的IOBUF为例,OBUFT为一个三态门,T是控制端,当信号作为输出,信号走向为红色路线,当作为输入,OBUFT关断,信号走向为蓝色路线。

IOBUF IOBUF(

.I(要输出的信号),

.O(外部输入的信号),

.T(三态控制),

.IO(外部引脚)

);

//综合后的电路如下图所示