本文转载来自:

其它内容参考:

个人理解的几点,先记录在这。

- DDR,全称Double Data Rate,双数据速率。即上下时钟沿采样。

- 双通道,是指两个channel,每个channel有单独控制器。比如SOC/CPU的ddr接口是64bit位宽,两个channel都是32bit位宽即可。因为依赖channel独立DDR控制器,可以并行采样,互不干扰,所以能达到双倍DDR位宽效果。台式机都是采用双通道DDR。

- 为什么SOC不用双通道DDR技术?个人理解,管脚多了,布线复杂,功耗也会上去。没有便携,小型化需求,成本比重等考虑是可以用双通道的。

- 本文没说DIMM和rank的区别。DIMM是插槽技术,rank是指8个chip芯片颗粒组合而成,与CPU/SOC DDR位宽保持一致的。

转载正文

bank、rank、channel这些关于内存的名词是否已困绕许久,疑似了解却又说不出个所以然来。 就让我们一步步拆解内存的面纱,从架构到读写方式逐步揭开内存的秘密。

标题挥发性内存分2种,SRAM和DRAM

RAM(Ramdom Access Memory)随机存取内存,之所以称作「随机存取」,是因为相较于早期的线性储存媒体(磁带)而言,因为磁带的存取是线性的,存取时间会依目前磁带位置和欲存取位置的距离而定,需转动磁带至应有的位置,距离越长、转得越久、存取时间也就越久。 而 RAM 没有这种烦恼,存取时间为固定值,不会因为数据在内存的位置而影响存取时间。

而 RAM 在电脑里又可大致上分为 2 种:SRAM 和 DRAM,两者的基础原理差不多,都是将电荷储存至内部,藉由改变不同的电荷储存 0 或是 1。 SRAM(Static Random Access Memory)静态随机存取内存和DRAM(Dynamic Random Access Memory)有着几点不同,SRAM的结构较复杂、单位面积的容量较少、存取速度快,DRAM则是构造简单、单位面积内的容量较多、存取时间较SRAM慢,同时DRAM也因为构造较简单的关系, 储存的电荷会随着时间渐渐消失,因此需要有个再充电(Refresh)的动作保持电容储存的数据。

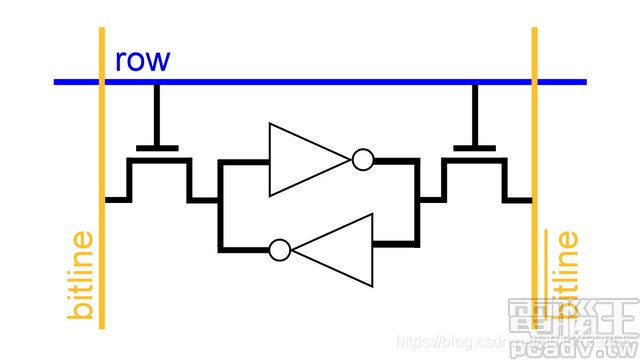

▲SRAM 单一位储存区的构造

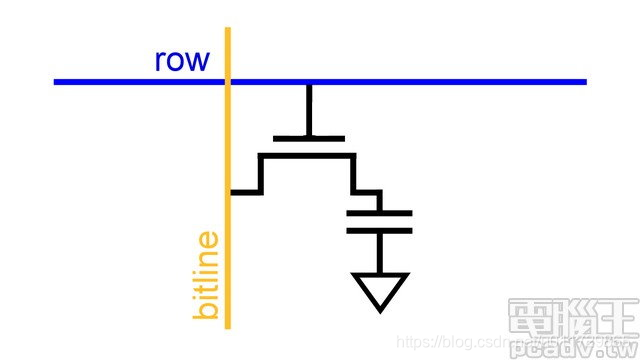

▲DRAM 单一位储存区的构造。

由图中SRAM和DRAM构造可得知,SRAM采用正反器(flip-flop)构造储存,DRAM则是采用电容储存。 因为 SRAM 和 DRAM 种种的特性不同,SRAM 适合作为暂存器和 CPU 缓取使用,DRAM 则是适合做为主内存或是其他设备间的快取使用。

挥发与非挥发性内存

挥发性存储器(Volatile Memory)和非挥发性内存(Non-Volatile Memory)之间的差异在于,断电之后是否可保存内部资料,挥发性存储器的数据会随着失去电力供应而消失,而非挥发性内存依然可以保有内部资料。

挥发性内存包含了SRAM和DRAM,而非挥发性内存包含ROM(Read-Only Memory)和Flash Memory闪存。

主内存子系统

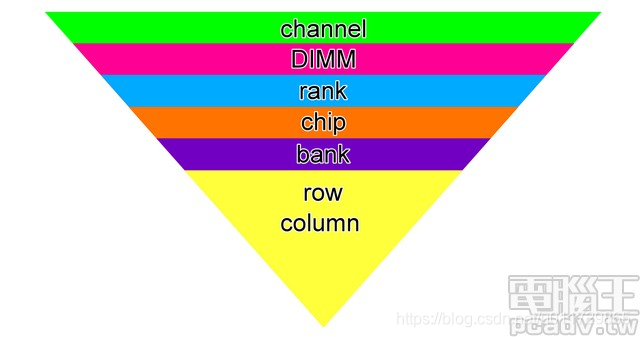

DRAM 由于制造简单、高密度,作为电脑内部的主内存再适合不过了。 但是由于主内存摆放在CPU之外,从工厂出来的晶粒需要封装和组合之后才可和CPU连结,因此从CPU至DRAM晶粒之间依据层级由大至小为channel>DIMM>rank>chip>bank>row/column,接下来就一一说明这些部分。

▲主内存由大至小,由上往下可做这样的拆分。

▲主内存从 channel 至 chip 的相对应关系。

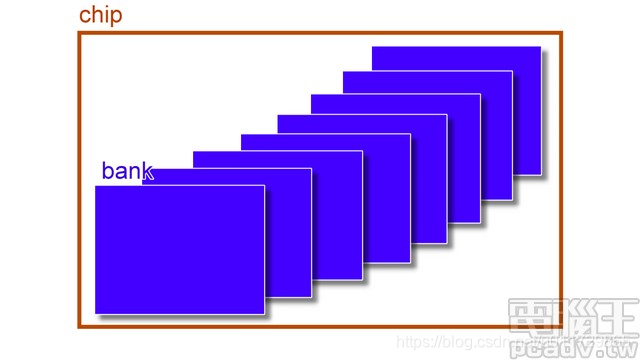

▲chip 往下拆分为 bank。

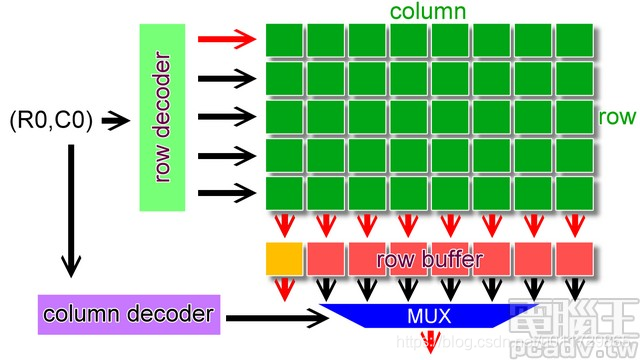

▲bank 往下拆就是 1 个个的储存单元,横向 1 排称之为 row,直向 1 排称之为 column,每排 column 的下方都有个 row buffer,用以暂存读出来的 row 排资料。

▲单一 DRAM 芯片的内部功能区块图(图片取自Micron)。

channel 和 DIMM

从内存控制器出来之后,最先遇到的就是 channel,每个 channel 需要配有 1 组内存控制器、2 个 channel 配置 2 组… 以此类推。 而每个 channel 中能够拥有许多组 DIMM(Dual In-line Memory Module),DIMM 也就是目前使用者能够在市场上买到的内存模块,因为多年前的主板必须购买内存颗粒(chip)直接插在主板上,而后发展出 SIMM(Single In-line Memory Module),将多组内存颗粒焊在 1 片电路板上, 成为内存模块,再将此电路板插在主板上。 接着为了增加数据吞吐量,将 1 条内存模块的带宽从 SIMM 的 32bit 改换成 DIMM 的 64bit,这设计依然沿用至今。

从内存颗粒过度到 SIMM 的时代,坊间出现了替用户将内存颗粒焊到 SIMM 电路板上的服务,因为当时内存非常昂贵,花一些小钱就可以把内存延用至新的电脑上。

rank 和 chip

rank 指的是链接到同 1 个CS(Chip Select)的内存颗粒 chip,内存控制器能够对同 1 rank 的 chip 进行读写操作,而在同 1 rank 的 chip 也分享同样的控制信号。 以目前的电脑来说,因为 1 组 channel 的宽度为 64bit,所以能够同时读写 8byte 的数据,如果是具有 ECC 功能的内存控制器和 ECC 内存模块,那么 1 组 channel 的宽度就是 72bit。

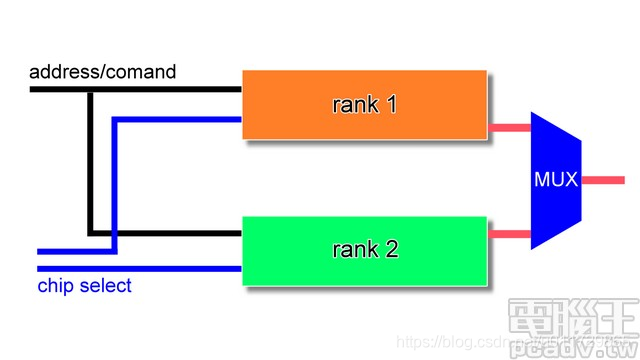

▲rank 1 和 rank 2 共享同组 address/comand 讯号线,利用 chip select 线选择欲读取或是写入的那一组,之后将资料经由 MUX 多工器送出。

有些人会有错误观念,以 chip 的数量或是以内存模块的单、双面进行 rank 的判断,但其实要以内存控制器和内存颗粒的规格进行判断,目前家用 PC 的内存控制器通道绝大部分都是 64bit 宽,内存颗粒则是 8bit 宽,因此 8 颗并联即可满足内存控制器的需求,也就是 1 组 rank。 但偶尔也有以 16bit 宽的内存颗粒制成的内存模块,此时 4 个 chip 就是 1 组 rank。

这在采用Intel H61/H81芯片组和传统单channel的主板时须特别注意,因为Intel限制H61/H81每个 channel仅能支持2组 rank,而不是4组 rank,部分主板每个 channel 又 做了 2 组内存模块插槽,造成部分用户同组 channel 放入 2 条内存模块时能够识别全部的内存容量(双面单 rank 的内存模块),部分用户则是仅能识别一半的容量(双面双 rank 的内存模块)。

bank、row、column

bank 再往下分拆就是实际储存位元的电路,一般来说横向选择排数的线路称为 row(row enable、row select、word line),直向负责传递讯号的线路为column(bitline),每组 bank 的下方还会有个 row buffer(sense amplifier),负责将独出的 row 资料暂存,等待 column 地址送到后输出正确的位,以及判断储存的数据是 0 还是 1。

▲1 个 bank 的读取操作。

▲1 个 bank 的写入操作。

内存的读写方式

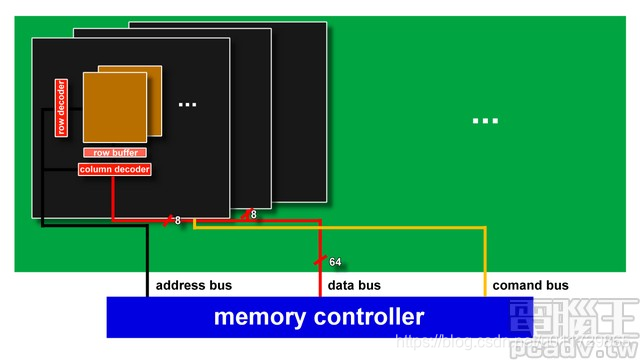

上图标明了内存的读写方式,读取时首先内存控制器会将 1 组地址由地址线传到内存上,控制线跟着传送控制信号;如果是多 rank 的安装情形,CS 也会送出对应的讯号选择目标 rank。 接着由于每个 rank 由许多 chip 组成,1 个 chip 仅负责部分的数据读取,chip 接收到地址信号后,将地址丢入内部的 row/column 解码器找出相对应的 bank 地址(每家每 款产品的内部 bank 组合有可能不同,因此对应也会有所不同),接着开启 row 线,同 1 排 row 的内部数据就会流到 row buffer 内部,row buffer 判断信号为 0 或是 1 之后就输出数据。

写入时除了地址资料外,还会传送欲写入的资料至芯片内部的 input buffer,同样的也是依照 row/column 解码器找出对应位置之后写入。

▲内存控制器和 DIMM 之间线路的关系。

越多越好,加速读写能力

家用计算机的内存控制器已经进入双通道内存控制器多年,加速原理为增加数据总线宽度,达到同时读写更多数据的能力。

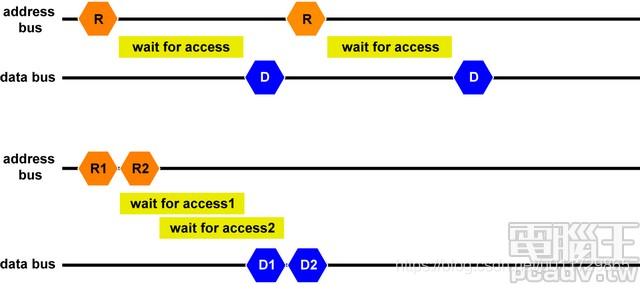

另一种增加带宽的方法就是减少延迟,利用多个 chip 或是 bank 达成。 一般的内存读取延迟为命令下达+内存读取延迟+输出数据,如果命令下达延迟为 2ns、内存读取延迟为 10ns、输出数据延迟为 2ns,那么读取 2 笔资料的总延迟就会是(2+10+2)×2=24ns。

如果现在能够将数据拆分至2颗内存上,那么2笔读取延迟将降低至16ns,因为不需等到前笔资料读取完成才发出下一笔的读取命令,在第一笔数据进入内存读取时即可发出。 这种概念也可应用到目前最夯的SSD上,较多CE(Chip Enable)封装的闪存芯片,通常都比较少CE封装的芯片来得快。

▲由时序图可得知,下方此种尽量分拆内存空间的作法,可大幅减少延迟。