80X86中断系统

- 能够处理256个中断

- 用中断向量号0~255区别

- 可屏蔽中断还需要借助专用中断控制器Intel 8259A实现优先权管理

1、中断的分类

中断可以分为内部中断和外部中断。

(1)内部中断

- 除法错中断

- 指令中断

- 溢出中断

- 单步中断

- 断点中断

(2)外部中断

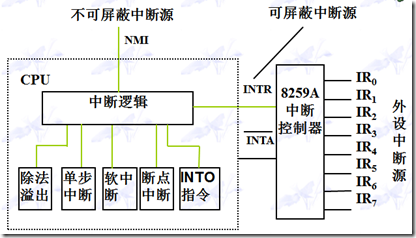

如果觉得上面的分类太抽象,那么下面的图会给你直观的印象。

通过这张图,我们可以明白,内部中断是在处理器内部产生。外部中断是通过两个信号线(NMI和INTR)引入处理器内部的。

2.内部中断

(1)除法错中断

在执行除法指令时,若除数为0或商超过了寄存器所能表达的范围,则产生一个向量号为0的内部中断,称为除法错中断。

例如:

mov bl,0

idiv bl ;除数BL=0,产生除法错中断

再比如:

mov ax,200h

mov bl,1

div bl ;商=200H,不能用AL表达,产生除法错中断

(2)指令中断

在执行中断调用指令INT n时产生的一个向量号为n(0 ~ 255)的内部中断,称为指令中断。

(3)溢出中断

在执行溢出中断指令INTO时,若溢出标志OF为1,则产生一个向量号为4的内部中断,被称为溢出中断。

(4)单步中断

CPU在执行完一条指令之后,如果检测到标志寄存器的TF位为1,则产生单步中断,单步中断的向量号为1.

(5)断点中断

主要用在程序调试中,向量号为3,利用“int3(指令机器码为0xcc)”这条指令设置断点,目的是显示断点前程序的执行结果。

注意:内部中断不受标志寄存器IF位的影响。

3.外部中断

(1)非屏蔽中断

通过非屏蔽中断请求信号向微处理器提出的中断请求,微处理器无法禁止,将在当前指令执行结束予以响应,这个中断被称为非屏蔽中断。

非屏蔽中断的向量号为2,非屏蔽中断请求信号为NMI

非屏蔽中断主要用于处理系统的意外或故障。例如:电源掉电前的数据保护,存储器读写错误的处理。

(2)可屏蔽中断

通过INTR引脚引入CPU,只有当中断允许标志位IF=1时,才能被CPU响应。通过8259A,一个系统中可有多个可屏蔽中断。

4.实模式下的中断向量表

(1)中断向量

中断向量就是中断服务程序的入口地址。它有两部分组成:

- 中断服务程序所在段的段基址(2个字节)

- 中断服务程序入口的偏移地址(2个字节)

(2)中断向量表

每个中断向量占4个字节,256种中断向量总共占用1024字节。在8086系统中,所有的中断向量按类型码存放于内存的最低地址(00000H~003FFH)的1K单元中。存放中断向量的这1K单元称为中断向量表。

中断向量在中断向量表中的位置=中断类型号×4

N*4的字单元存放偏移地址;

N*4+2的字单元存放段基址。

5.中断类型号的获取

(1)对于除法出错,单步中断,不可屏蔽中断NMI,断点中断和溢出中断,CPU分别自动提供中断类型号0~4。

(2)对于用户自己确定的软件中断INT n,类型号由n决定。

(3)对外部可屏蔽中断INTR,CPU从可编程中断控制器8259A中获得中断类型号。

说明:

8086有两个引脚可以接收外部的中断请求:INTR和NMI

- 当NMI(非屏蔽中断请求)引脚上出现上升沿信号时,CPU立即无条件(不执行中断响应周期,不受标志寄存器IF位的影响)地转入"2号中断处理程序"。

- 当INTR(可屏蔽中断请求)引脚上出现高电平信号时,若IF=0,CPU不响应中断请求。若IF=1,CPU响应中断请求。CPU响应中断时,首先执行"中断响应周期",以便从中断控制器8259获得中断类型码,然后根据中断类型码转入相应的中断处理程序。

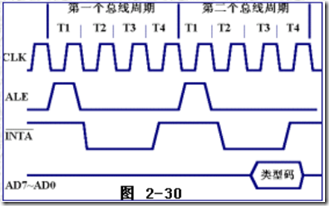

中断响应周期由两个总线周期构成

1.第一个总线周期

CPU向外设发出一个低电平的中断应答信号INTA*,表示已经接受申请,要求外设传送中断向量号

2.第二个总线周期

外设传送中断向量号,CPU在T4的下降沿采样数据总线,读入外设传送来的中断向量号(如下图)

6.中断过程

(1)中断请求

中断源向CPU发出请求中断信号。中断信号将被锁存,直到CPU响应中断后,中断请求信号才被清除。

(2)中断响应

CPU在执行每条指令的最后一个时钟周期检测中断请求信号。若发现中断请求信号有效,在允许中断的条件下,CPU响应中断。

响应中断的过程可以总结为:

- 取得中断类型码N;

- pushf

- TF=0,IF=0

- push CS

- push IP

- IP=N*4, CS=N*4+2,;转中断服务程序

7.中断处理程序和iret指令

中断处理程序的编写方法和子程序比较相似,下面是常规的步骤:

(1)保存用到的寄存器

(2)处理中断

注意:由于IF标志被设置为0,在中断处理中,处理器将不再响应硬件中断。如果希望更高优先级的中断嵌套,可以在编写中断处理程序时,适时用sti指令开放中断。

(3)恢复用到的寄存器

(4)用iret指令返回

iret指令的功能可以用汇编语法描述为:

pop IP

pop CS

popf

需要说明的是:中断向量表的建立和初始化工作是由BIOS在计算机启动时完成的。BIOS为每个中断号填写入口地址,因为它不知道多数中断处理程序的位置,所以一律将它们指向同一个入口地址,在那里只有一条指令:iret. 也就是说,当这些中断发生时,只做一件事情——立即返回。当计算机启动后,操作系统和用户程序再根据自己的需要,修改某些中断的入口地址,使它指向自己的代码。

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)