之前准备了一段时间的秋招,好久没有学SDC,现在准备SDC和秋招同时准备,更新。

- 一个复杂的设计都需要多个时钟信号来共同完成功能,设计中异步时钟不能共享确定相位关系的时钟信号,也不必过于关心其时钟源,但是同步信号往往产生于同一个时钟源(如时钟分频器、时钟乘法器、时钟门控)

- 不同模块运行在不同时钟下,如果不考虑各自关系,将会带来异步性的设计问题。

时钟派生方式

- 时钟分频器就不过多说了,无非是用DFF做counter完成N分频。

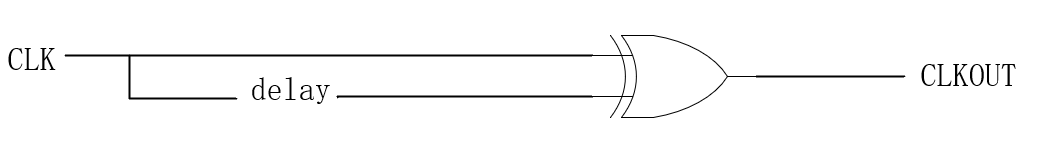

- 时钟乘法器在此介绍一下,我们在设计中常用PLL完成倍频的需求,但是同样可以通过缓冲器和反相器引入delay,再结合XOR完成倍频。

如上图所示,通过buffer和inv完成对源时钟的延时,再将延时后的时钟和源时钟一同输入XOR,便可以完成倍频的功能,但是buffer和inv需要仔细计算过delay time。

- 时钟门控,这种方式主要通过使能信号来控制时钟是否对后级起作用,虽然时钟信号一样,但是对电路来说时钟源并不一样。(时钟门控常用于低功耗设计中)

create_generated_clock

在SDC中,用于设定生成时钟的命令是create_generated_clock,而它的设计对象可能是pin、port或net.

- 设定生成时钟的源引脚可用 -source选项。(此处需要注意源对象和生成时钟源之间的区别,源对象是指生成时钟设定在哪个位置,而生成时钟源指哪个是参考信号)

- 只要定义了generate clock,则开发工具将基于source clock派生时钟特性(周期、波形等)

- 和create_clock一样,用-name表征每个clock的名字,每个generate clock同样要有唯一的name

- 设定生成时钟的特性如:-edges、-divide_by、-multiply_by

edge divide multiply

edge通过指定波形边沿的变化来描述generate clock。

divide_by和multiply_by通过直接对源时钟的分频,倍频来描述generate clock

对上述电路,分别用edge、divide_by、multiply_by对其约束

create_clock -period 10 -name CLK [get_ports CLK]

create_generate_clock -name LSB -source [get_port CLK]

-divide_by 2 [get_pins FF1/Q]

create_generate_clock -name MSB -source [get_pins FF1/Q]

-divide_by 2 [get+pins FF2/Q]

create_generated_clock -name LSB -source [get_ports CLK]

-edges [1 3 5][get_pins FF1/Q]

create_generated_clock -name MSB -source [get_pins FF1/Q]

-edges [1 3 5][get_pins FF2/Q]

不同的分频时钟约束与上述约束类似。

edge_shift

- 除此之外,还可以用**-edge_shift**描述每个边沿的相位偏移,例如

create_generated_clock -name CLKOUT -source [get_ports CLK]

-edges[1 1 3] -edge_shift[0 2 0][get_pins X]

上面的指令表示:

- 在source clock的第一个边沿产生上升沿

- 在source clock的第一个边沿后2ns产生下降沿

- 在source clock的第三个边沿产生上升沿

多同源时钟

下图是一个基于三分频电路的时钟切换电路。

电路输入的mux会决定最后分频的divide clk对应的是clk1还是clk2,这就导致generate clock的source clock不同,所以写约束时要注意一些。

create_clock -name C1 -period 10 [get_ports CLK]

create_clock -name C2 -period 15 [get_ports CLK] -add

#C1

create_generated_clock -name GC1 -divide_by 3 -source [get_port CLK]

-master_clock C1 [get_pins FF2/Q]

#C2

create_generated_clock -name GC2 -divide_by 3 -source [get_port CLK]

-master_clock C2 [get_pins FF2/Q] -add

如果用户要得到两个生成时钟的STA,需要添加-add,否则后一个会覆盖前一个。

而master_clock用于定义哪些时钟与用于派生generate clock的特定源对象关联。

使能组合路径

- 在设计中会出现时钟随着数据作为输出,这种结构的优点时时钟和数据按同样的路径来传送,如下图:

- 如果有些路径在本质上时时序电路,即他们通过时序电路单元,则generate clock通常无损,但是如果时组合逻辑和时序逻辑的混合,那么会出现时钟失效的情况,这时候需要**-combinational**约束来阻隔时序电路。

create_generated_clock -name CLKOUT -combinational

-source [get_pins FF1/Q] [get_ports CLKOUT]

其他注意事项

- 一个遗漏的generate clock将会产生无约束寄存器

- 需要保证generate clock 设置了source clock

- 如果时钟收敛于多种路径,则特别注意禁用时序电路路径

搜索关注我的微信公众号【IC墨鱼仔】,获取我的更多IC干货分享!