功能

1. 单axi-stream 接口输入(10bit raw输入),axis输出(10bit输出)。

2. 使用xilinx hls 编写。

3. 配置寄存器有

目前最多画10个框

#pragma HLS INTERFACE s_axilite port=width

#pragma HLS INTERFACE s_axilite port=height

#pragma HLS INTERFACE s_axilite port=startx

#pragma HLS INTERFACE s_axilite port=starty

#pragma HLS INTERFACE s_axilite port=widthx

#pragma HLS INTERFACE s_axilite port=heighty

输入图像

输出图像

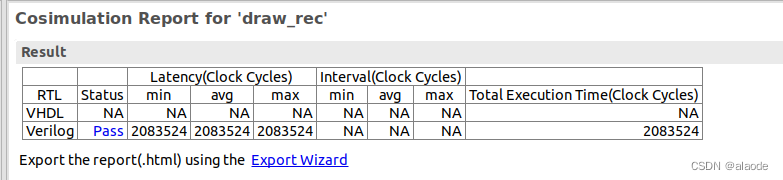

4. 仿真