首先创建一个模块为test

目录为这样:

在模块test中写入:

module test(a,b,c);

input a,b;

output c;

wire d,e;

assign c = a&b;

and a1(d,a,b);

or a2(e,a,b);

rt pin(

.a(a),

.b(b),

.c(d)

);

rt pin_tr(

.a(a),

.b(b),

.c(e)

);

endmodule

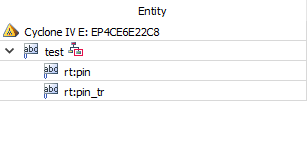

编译后,目录变为:

再flie->new一个rt的模块

写入:

module rt(a,b,c,d,e);

input a,b,c;

output d,e;

reg d,e;

always@(a | b | c)

begin

d = a & b;

e = a | c;

end

endmodule

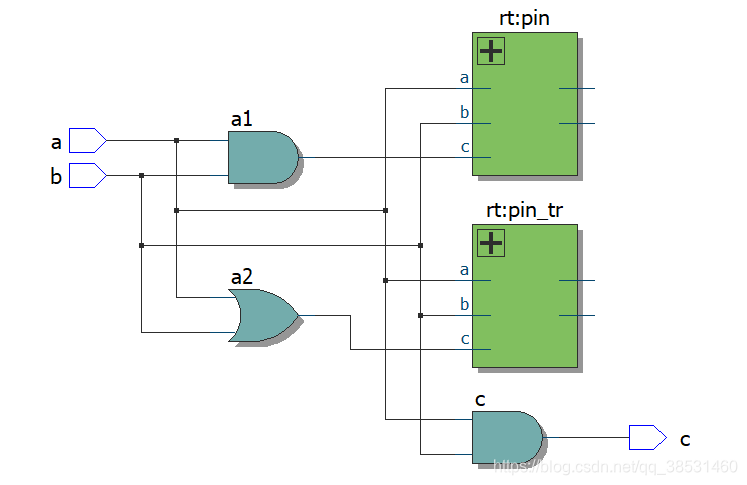

再编译后:点击:rtl viewer

生成的模块图为: