扩频运算,宏观上看,是把一个比特的0或1,扩展成8比特,起到了扩频的效果,从效果上理解扩频,没有多大的问题。

但为什么要把预先把1转换成+1,0转换成-1才能运算? +1,-1转换的本质是什么?

不要小看这个不起眼的转换,它涉及到数字无线通信中的一个核心问题:调制技术,即如何通过无线电磁波传递比特0和比特1的二进制数据。

理解这个问题的本质,对于理解扩频与数字调制映射、高频调制的相互间的位置关系,以及再进一步探讨如何通过扩频实现码分多址的多用户复用起着关键性的作用。

原因1:二进制比特运算不支持数值信息的叠加

扩频运算,宏观上看,是把一个比特的0或1,扩展成8比特,起到了扩频的效果,从效果上理解扩频,没有多大的问题。

但从实际数学的运算和系统实现来看,是有问题的,因为二进制比特本身的运算并不支持信息的叠加!

比特位的最大值为1,最小值为0,二进制比特叠加后,原有的信息会消失。

而实数的加法叠加运算,信息会被保留在叠加后的数值中。

原因2:区别“0数据”与“无数据”的需要

在计算机中,逻辑0用低电平表示,逻辑1用高电平表示。

在数字无线通信中,数字调制技术解决的是如何通过无线电磁波传递比特0和比特1的二进制数据。“0”和“1”都表示有数据,0不表示没数据,0本身就是数据。如果还用低电平表示0,高电平表示1,那么如何表示“无数据”呢?

0电平意味着无电信号,用于表示“无”数据最理想不过了,这就需要为“0” 定义一个新的电平信号:负电平,即-1.

逻辑1:正电平+1,这里的+1,代表的是正电平单位,实际的电信号可能是+5V, 3.3V, 2.5V, 1.8V或其他任意幅度的正电压。

逻辑0:负电平-1,这里的 -1,代表的是负电平单位,实际的电信号可能是-5V, -3.3V, -2.5V, -1.8V或其他任意幅度的负电压。

无数据:0电平0,这里的0, 代表“无”电信号。

原因3:数字调制的需要

数字调制技术解决的是如何通过无线电磁波传递二进制比特0和比特1的二进制数据,数字调制的本质是通过离散的数字电信号控制高频载波信号的参数:幅度、频率、相位。简单的代表1和0的高电平1、低电平0,不足对电磁波的参数进行复杂控制,特别是多进制调制。因此,在数字调制过程中,需要预先把逻辑的二进制比特,预先映射特定的能够控制高频载波信号参数的数字信号!在上图中,体现在二进制比特映射模块。

至于二进制比特映射成什么样的数字电信号,取决于不同的数字调制技术以及不同的实现方法。如2进制BPSK调制、4进制QPSK、8进制8QPSK调制映射的数字信号就不相同。

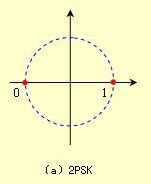

BPSK:

二进制比特1 =》 正电平数字信号,用数字+1表示。

二进制比特0 =》 负电平数字信号:用数字-1表示。

无数据: =》 0 电平数字信号:用数字0表示。

QPSK:

A可以是1V, 也可以是0.5V, 可以是任意电压值。

因此,扩频运算和码分多址运算,不是对二进制比特进行运算,而是对二进制比特映射后的数字信号进行运算,是对数字信号的幅度值进行运算!

备注:

数字信号:指自变量是离散的、因变量也是离散的信号,这种信号的自变量用整数表示,因变量用有限数字中的一个数字来表示。比如1,2,3,4,5,6,7,8,9,10...都是数字信号,0.7,0,8, 0.9,1.0,1.25也都是数字信号。

二进制:在数学和数字电路中指以2为基数的记数系统,以2为基数代表系统是二进位制的。这一系统中,通常用两个不同的符号0(代表零)和1(代表一)来表示 [1] 。数字电子电路中,逻辑门的实现直接应用了二进制,因此现代的计算机和依赖计算机的设备里都用到二进制。每个数字称为一个比特(Bit,Binary digit的缩写)