基于spyglass同步设计分析和静态验证 - 豆丁网

http://www.docin.com/p-1444334021.html

这篇论文,讲述了跨时钟问题的原理、实例分析及使用spyglass解决CDC(clock domain crossing)的办法。对于我来说,有很多参考价值。特此作一阅读笔记。作为以后不断精进的知识储备。

常见的CDC问题

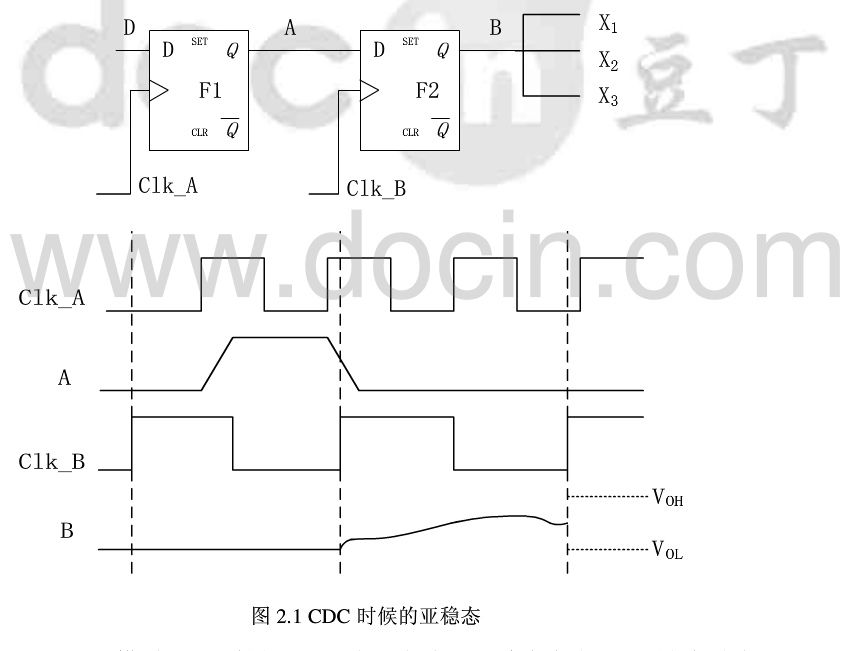

亚稳态

建立保持时间违反,就会发生亚稳态。

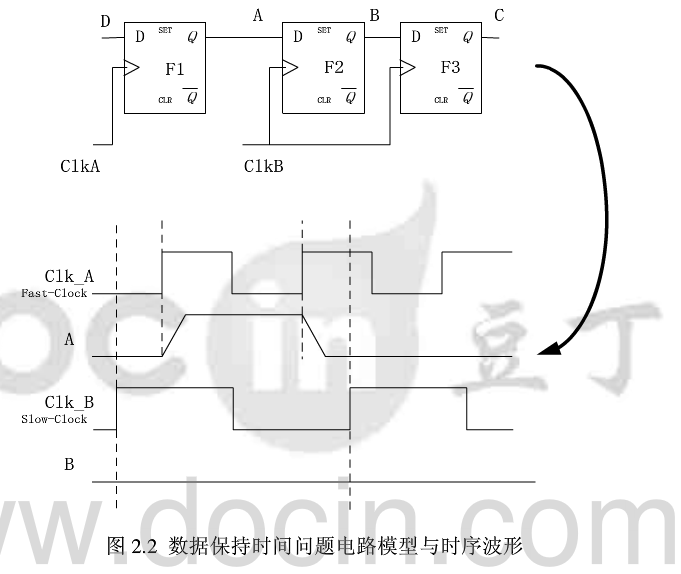

data hold,数据保持的时间问题

这种情况,发生在快时钟到慢时钟域。由于快时钟域的数据信号,保持时间过短,不能被慢时钟域采样到。

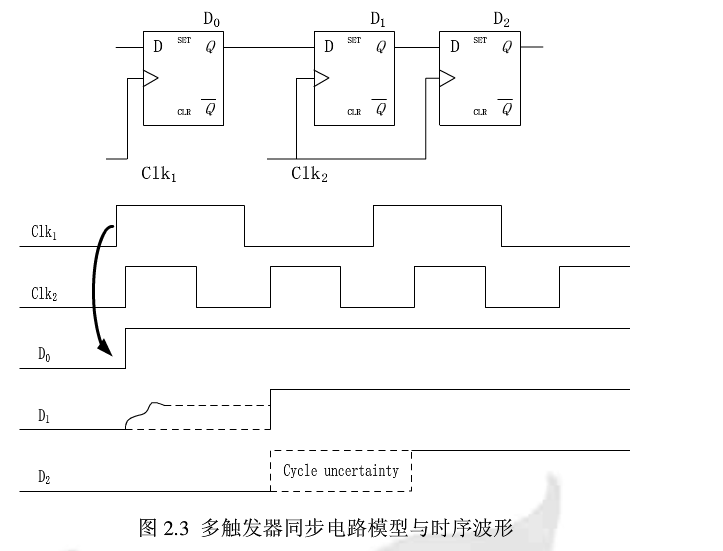

常见的两级触发器同步

周期内存在亚稳态问题。所以两级触发器同步结构中,第一级触发器的输出,设计中是不允许参与任何组合逻辑的。

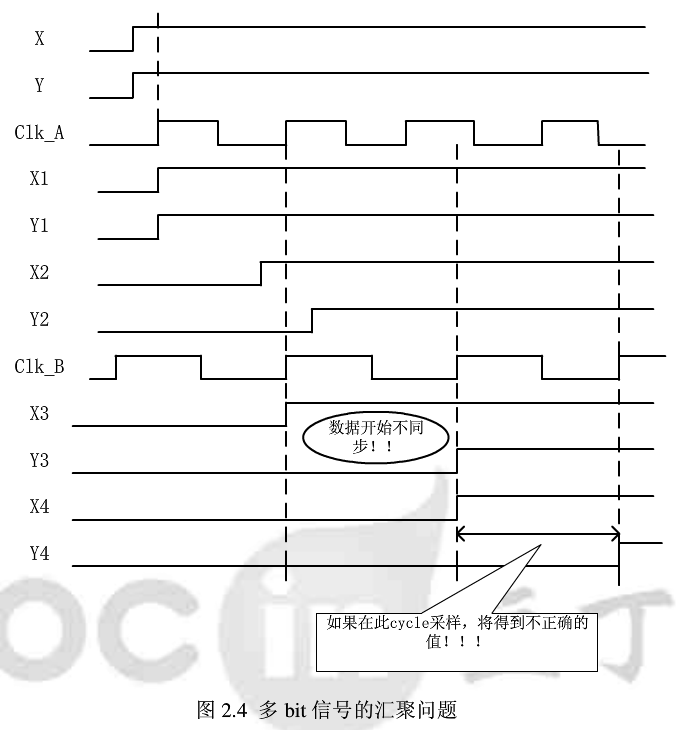

多bit信号,采用简单的两级触发器同步

这种设计是有问题的。会使得输出状态存在不可预期的一组或多组值。如果格雷编码后,再经过下述逻辑结构,能够保证输出状态不会存在不可预期的一组或多组值;一般会用到状态机的同步。

CDC中复杂的同步设计

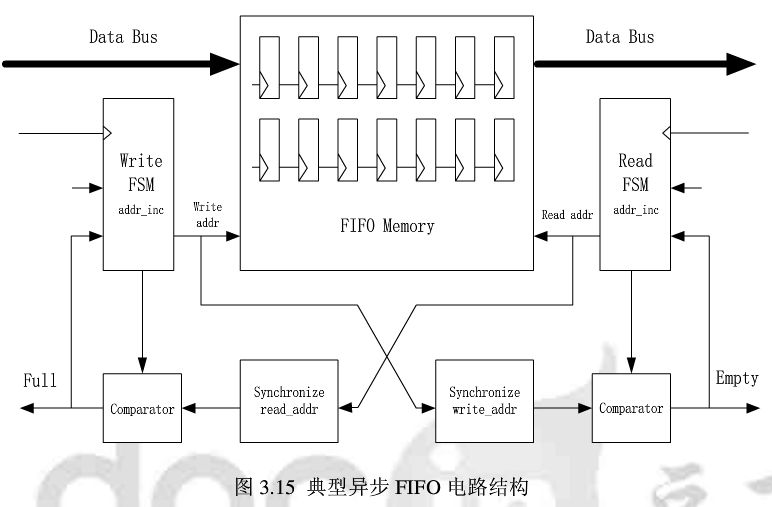

- 异步fifo

- 握手协议的同步

- 单一使能信号形式的同步

亚稳态总会有概率的存在

这是因为触发器的亚稳态,无法在期望的时间范围内得到恢复。而且亚稳态会传递至后续的电路中。

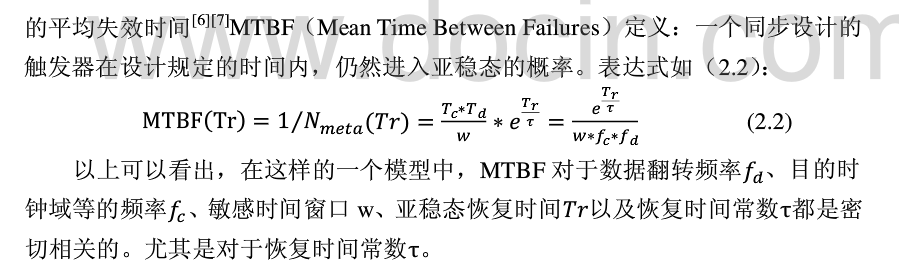

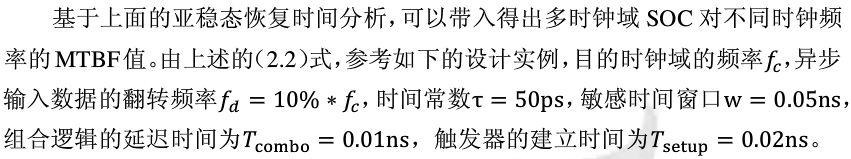

这就引出了同步设计中的平均失效时间MTBF(Mean Time Between Failures);定义是:一个同步设计的触发器在设计规定的时间内,仍然进入亚稳态的概率。

其中亚稳态恢复时间=目的时钟域的周期-(组合逻辑的时间+Tsetup);理解来说就是亚稳态可以恢复的有效时间;超出这个亚稳态恢复时间,就会产生亚稳态的危害。

根据公式,可以看出,数据翻转率越低,目的时钟域频率越低、建立保持窗口越小;都会增加MTBF,即改善亚稳态的概率。增加亚稳态恢复时间,也可以改善亚稳态的概率。

由此,得出二级同步触发器结构的亚稳态恢复时间=目的时钟域的周期-(Tsetup);因为两级触发器的组合逻辑时间为0.

同理,得出二级同步触发器结构的亚稳态恢复时间=2*目的时钟域的周期-(Tsetup)。

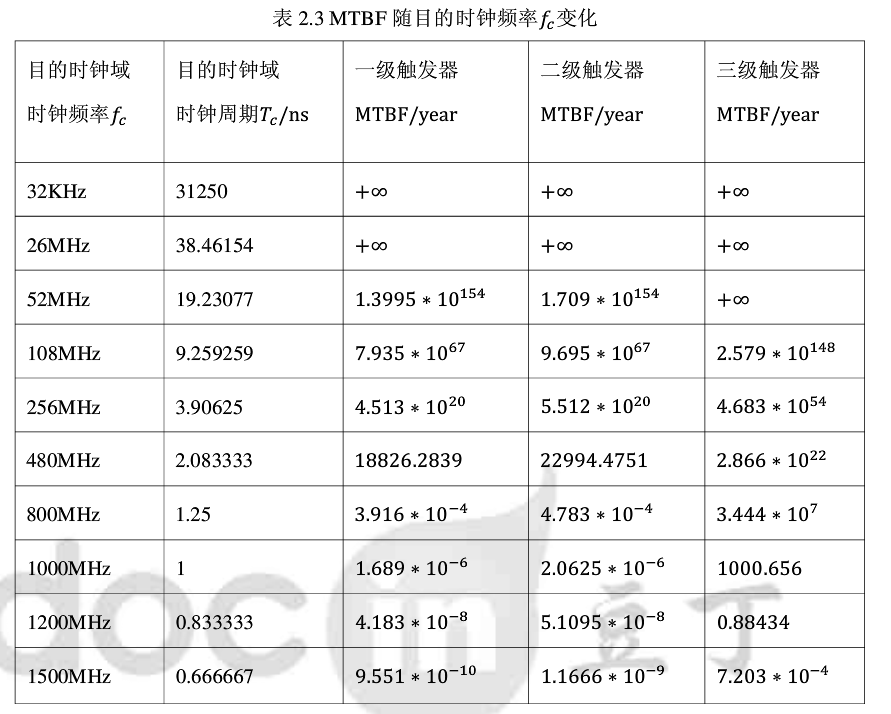

所以,由上图可以得知,800MHz以上,出现亚稳态错误的几率会非常高,平均约3.43小时出现一次。而480MHz以下的时候,2.2994万年才会出现一次。所以,大于480MHz以上,就不要用二级触发器做同步了。

另外,三级同步触发器,只能改善,但是随着时钟频率的不断提高,仍然存在危险;而且会增加系统的总体延迟。

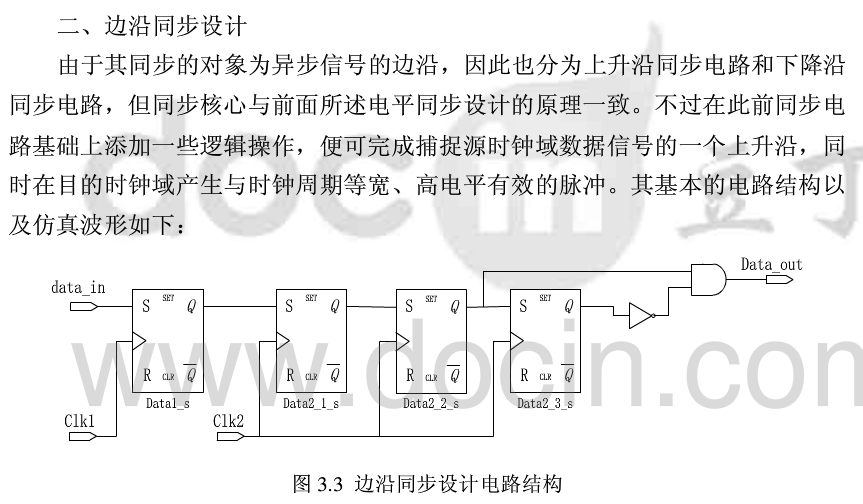

PS:

这里,可以看出上面的概率,也许会因为这个常量,在不同环境里导致概率增大的情况。

单bit信号的CDC同步设计

慢时钟域到快时钟域的同步情况

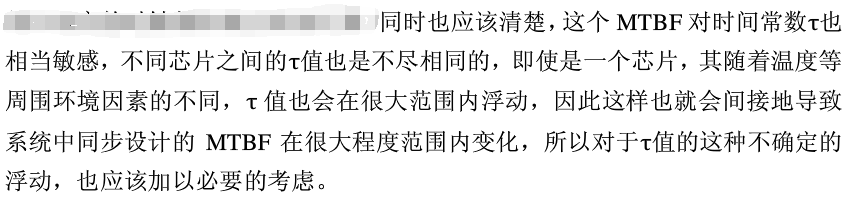

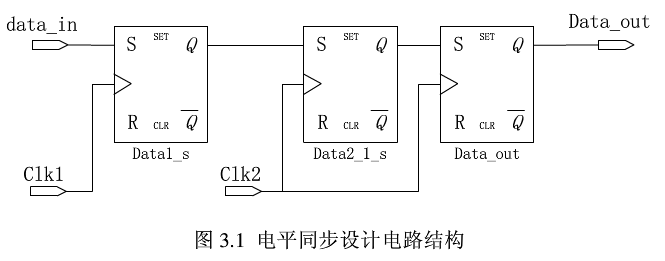

有两种传输类型,一种是电平敏感的同步设计;一种是边沿敏感的同步设计。

原文介绍,异步输入信号必须满足一定的保持时间,这一点没理解。

当目的时钟域与源时钟域小于两倍的情况下,单bit的异步输入信号必须保持至少两个源时钟域的周期,这样才能不会产生数据的丢失情况.

快时钟域到慢时钟域的同步情况

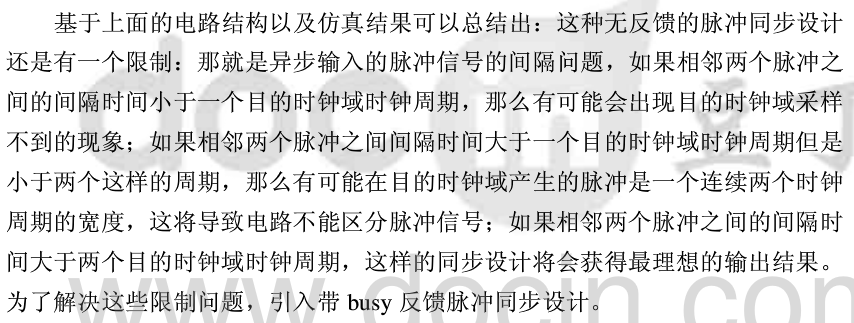

这种结构,存在限制。

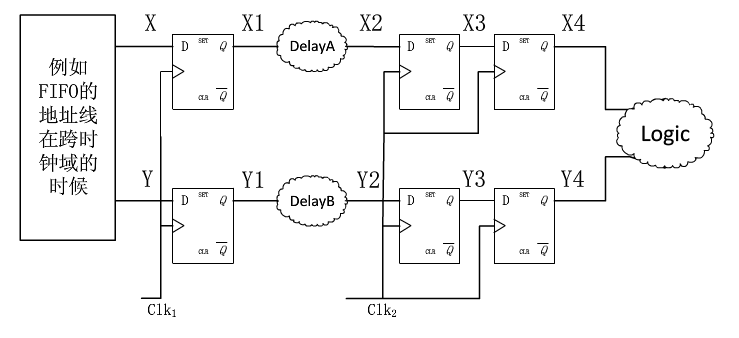

多bit信号的CDC同步设计

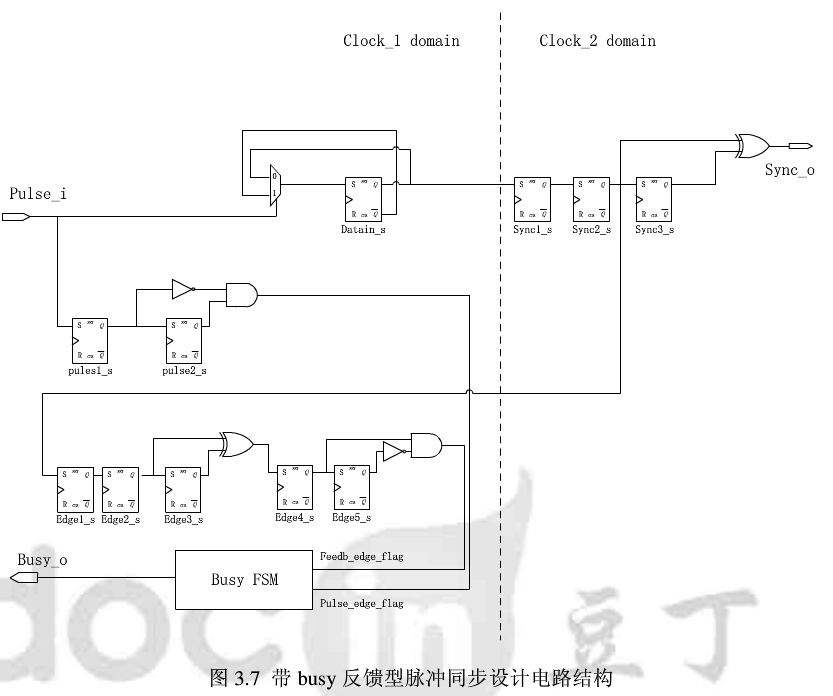

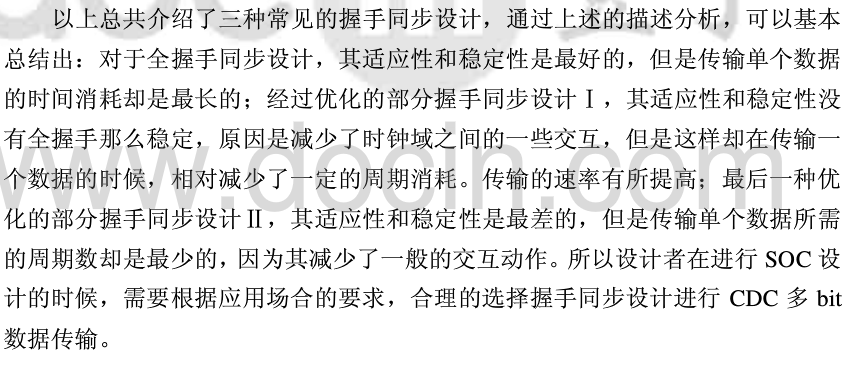

握手协议同步设计

具体实现,有三种握手同步设计。这里不再赘述,详情看参考文件。

异步fifo的同步设计

看文档的意思,是说异步fifo能完美解决异步处理。但是还没理解深入,待续。

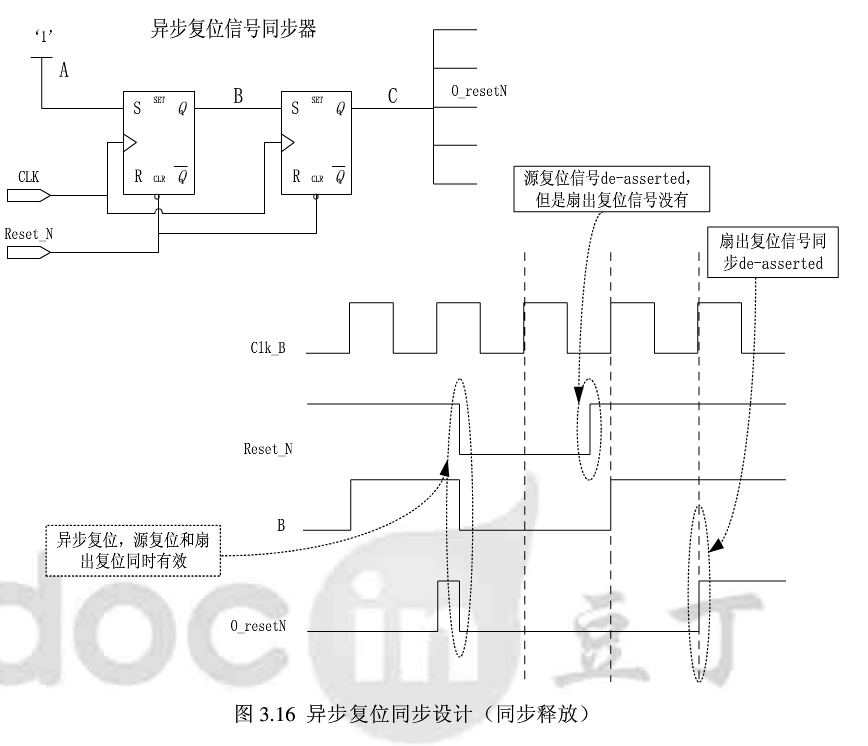

异步复位信号的同步设计

不过要注意,同一个异步复位信号,不要多次做上述结构。可能是因为上图中的第一个异步复位宽度已经很窄,无法再执行一次同步设计吧?!

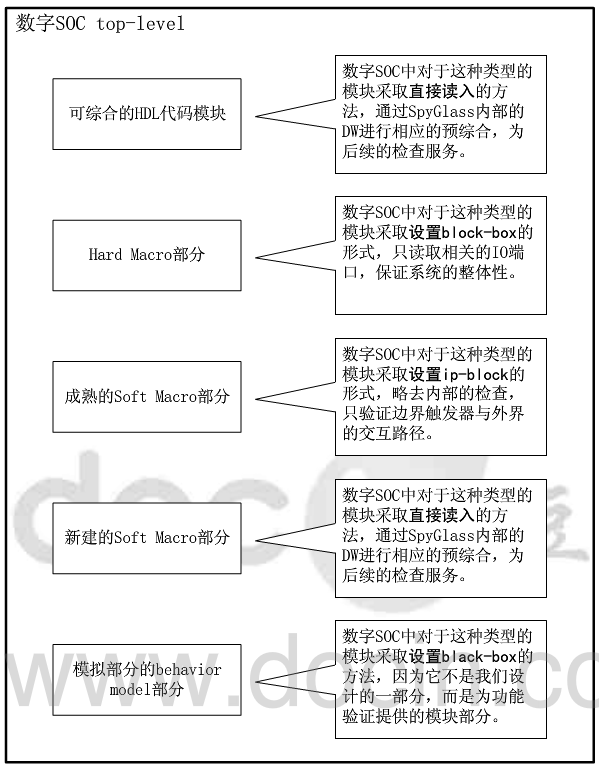

spyglass工具的引入

spyglass类似pt,是静态验证工具。特点就是不需要编写testbench,就可以验证。

这里可以结合spyglass的理解,进行演示脚本的执行过程。

组合逻辑的输出,不要直接用于异步处理。

因为会出现毛刺,解决办法,就是组合逻辑的输出,加一个触发器在源时钟域下采样一次。