Chapter 55 Zipwire

55.1 Chip-specific Zipwire information

本节总结了控制器中的模块配置。 关于 SIPI 和 LFAST 的全面介绍,请参考 SIPI 和 LFAST 的具体专用章节.

SIPI 和 LFAST 相互连接并作为一个单元出现。 两个模块的 LFAST 部分允许高速设备间通信。

SIPI 允许在具有 SIPI 和 LFAST 通信模块的设备之间共享内存(参见图 55-1)。 Zipwire 是 LFAST 和 SIPI 组合的官方品牌。

LFAST 可以在从模式配置或主模式配置中运行。 在主模式下运行的节点控制串行链路,但在主模式和从模式下,SIPI 可以同时充当 SIPI 命令的发起者和目标。 有关模块配置和功能的详细信息,请参阅 SIPI 和 LFAST 章节。 SIPI 芯片 ID = 098D801D。

52.2 Overview

SIPI 和 LFAST 模块作为一个称为 Zipwire 的单元一起工作。 两个模块的 LFAST 部分允许高速设备间通信。 SIPI 允许在具有 SIPI 和 LFAST 通信模块的设备之间共享内存。

LFAST 可以在从模式配置或主模式配置中运行。 在主模式下运行的节点控制串行链路,但在主模式和从模式下,SIPI 可以同时充当 SIPI 命令的发起者和目标。 有关模块配置和功能的详细信息,请参阅 SIPI 和 LFAST 章节。

55.3 Introduction

Zipwire 是一组模块,允许一个 MCU 具有快速、低引脚数的串行通信链路,直接连接到另一个 MCU 或智能 ASIC 的内存映射外设和/或内存。 Zipwire 在硬件中实现,因此启动器或目标节点没有 CPU 负载。 Zipwire 支持 8 位、16 位或 32 位读取和

写入目标节点的任何 32 位地址。

Zipwire 架构是完全流水线的,并支持多个未完成的命令,以最大限度地利用串行链路带宽。

串行链路使用 LVDS 物理层高速运行。 一对 LVDS 用于 Tx,另一对用于 Rx,带有一个单独的 LFAST 参考时钟,总共五个引脚。

Zipwire 还支持用于传输大块数据的流模式。

在流模式下,Zipwire 具有很高的传输速率。

55.4 Zipwire Block Diagram

图 55-2 显示了使用五线接口连接 Zipwire 的两个 MCU。 两种 MCU 都支持 Zipwire 的目标和启动器模式。 SIPI 总线主接口用于所有目标模式事务。 SIPI 注册接口用于所有发起方事务和初始设置。 LFAST 寄存器接口用于初始设置。

该图显示了来自 MCU B 时钟系统的 LFAST 参考时钟。 Ref_Clock 可以来自任一 MCU。 它是用户可配置的,但它必须是驱动两个 LFAST 模块的相同时钟。

55.5 Architecture

Zipwire 由几个模块和系统资源组成。 物理层是具有共模电压和定义摆幅的 LVDS。

传输层是一种称为 LFAST 的协议。 LFAST 是一个异步协议,使用不归零编码。 LFAST 协议由以下部分组成:

- 一个固定的 16 位同步帧,允许接收器检测最佳点以对输入数据进行采样。

- 后跟一个 8 位 LFAST 标头,它定义了通道号和 LFAST 有效负载的大小。

- 最后是有效载荷,可以在 8 到 288 位之间。

应用层协议称为串行处理器间接口 (SIPI)。 SIPI 在 LFAST 之上运行,并完全封装在 LFAST 有效负载中。 SIPI 在 Zipwire 中使用四种固定大小的 LFAST 有效负载:

• 32-bit

• 64-bit

• 96-bit

• 288-bit

SIPI 协议实现了一组由一个 MCU 发起的命令,用于在另一个连接的 MCU 中读取和写入任何 32 位地址位置。 SIPI 协议允许一个或两个 MCU 发起命令。该协议还支持从一个 MCU 到另一个 MCU 的中断请求。

SIPI 模块实现了协议的发起者部分和协议的接收者部分。该模块实现了四个 SIPI Initiator 通道,它们可以相互独立运行,也可以同时运行。 SIPI 模块是低速 XBAR 上的总线主控器。作为来自启动 MCU 的命令的目标 MCU,SIPI 可以对目标 MCU 内的任何地址位置执行读写访问。

在本地 MCU 上运行的软件应根据需要配置系统 MPU 以允许/拒绝对 MCU 内存和资源的内存访问。

模块的启动器部分连接到 DMA 控制器,并能够在命令完成时生成 DMA 请求。这允许一系列读取或写入命令在 Initiator MCU 中排队并由 DMA 和 SIPI 执行,而无需 CPU 干预 Initiator 或 Target MCU。

55.6 Zipwire interconnections

LFAST 有以下连接:

• Tx 和Rx 配置由LFAST 控制寄存器控制。

• 外设桥接接口 (PBRIDGE) — 允许软件读取和写入配置寄存器。

• Tx 数据端口/Rx 数据端口 — 直接连接到 SIPI 模块。 允许将接收到的数据有效地传输到 SIPI 并传输要从 SIPI 传输的数据。

• 中断请求连接— 允许模块在需要服务时向CPU 进行标记。

SIPI 具有以下连接:

• 外设桥接接口 (PBRIDGE) — 允许软件读取和写入配置寄存器和 SIPI 接口寄存器。

Zipwire 性能:

• DMA 连接——允许 SIPI 命令序列在没有 CPU 干预的情况下排队和启动。

• Crossbar 主端口 — 允许 SIPI 执行请求的命令以读取和写入 MCU 地址空间。

• Tx 数据端口/Rx 数据端口— 直接连接到LFAST 模块。 允许从 LFAST 有效传输接收到的数据,并将要传输的数据传输到 LFAST。

• 中断请求连接— 允许模块在需要服务时向CPU 进行标记。

55.7 Zipwire 性能

性能考虑两个方面:

• 带宽— 在两个节点之间可以读取或写入数据的速率。 它假设来自 Initiator 节点的读取或写入命令可以以 Target 节点可以使用这些命令的最高速度连续发送。

• 延迟——从发起者节点发送读或写命令到主节点的时间。

发起者节点接收回读数据或写确认。

Table 55-1. Zipwire performance parameters

55.7.1 Read performance

Zipwire 读取操作包括三个阶段:

• 发起者向目标发送SIPI Read 命令。

• Target 解析接收到的命令并运行主总线周期来读取数据。

• Target 将 SIPI Read 响应发送回 Initiator。

Zipwire 读取请求帧包括:

Zipwire 读取响应包括:

A Zipwire read operation consists of the following stages:

Initiator node: Sends read command

• Sends SIPI read command to target.

• LFAST Tx transmits the frame = (l1 + f1) * d

Target node: Processes read command

- LFAST target parses the received command and sends the command and address to

SIPI via its Rx FIFO = (2 * d - SIPI parses the command and calculates the CRC = (sf1+ s1) * y

- SIPI initiates single-beat word read transfer on the master bus = (r * x)

Target node: Sends read response

- SIPI transmits read response frame to the LFAST Tx FIFO = (s2 * y)

- LFAST transmits the SIPI frame sequentially to the initiator= (l3 + f2) * d

The time to run the master bus cycle will vary depending on the memory being read:

• Time for initiator node to send read command: (l1 + f1) * d = A1

• Time for target mode to read an address location is:(l2 * d) + ((sf1+ s1) * y) + (r * x) = Z1

• Time for target mode to send a read response: (s2 * y )+ ((l3+f2) * d) = B1

Total read performance: A1 + Z1 + B1

55.7.1.1 Read bandwidth

Zipwire 目标节点最多可以有两个未完成的帧。 因此,目标节点可以同时接收命令,处理命令,但除非收到读取响应,否则无法发送新的读取命令。

传输命令或响应的时间少于处理命令的时间。 因此,带宽受限于处理消息和发送另一个读取请求的时间 Read Bandwidth = 4 bytes in ns

55.7.1.2 Read latency

延迟是发送读取命令、处理命令和发送读取响应所需的时间。

55.7.2 Write performance

Zipwire 写操作包括三个阶段:

• 发起者向目标发送SIPI 写命令。

• Target 解析接收到的命令并运行主总线周期来写入数据。

• Target 将SIPI Write 响应发送回Initiator。

Zipwire 写入命令包括:

Zipwire 流写入命令包括:

Zipwire 写确认包括:

Zipwire 写操作包括以下阶段:

Initiator node: Sends write command

- SIPI sends a write frame to target

- LFAST Tx transmits the frame = (l4 + f3) * d

Target Node: Processes write command

3. LFAST target parses the received command and sends the command, address and data to SIPI via its Rx FIFO = l5 * d

4. SIPI parses the command and calculates the CRC = (sf2 + s1) * y

5. SIPI initiates single-beat write transfers on the master bus = n * w * x

Target Node: Sends Write-acknowledgement frame

6. SIPI transmits Write-acknowledgement frame to the LFAST Tx FIFO = (s3 * y)

7. LFAST transmits the SIPI frame sequentially to the initiator= (l6 +f4) * d

The time to run the master bus cycle will vary depending on the memory being written:

• Time for initiator node to send write command: (l4 + f3) * d = A2

• Time for target mode to write address location(s) is: (l5 * d) + ((sf2 + s1) * y) + (n *w * x) = Z2

• Time for target mode to send a read response: (s3 * y) + ((l6+f4) * d) = B2

Total Write performance: A2 + Z2 + B2

55.7.2.1 Write bandwidth

Zipwire 目标节点最多可以有两个未完成的帧。 因此,目标节点可以同时接收命令、处理命令,但除非收到写确认,否则无法发送新的写命令。

发送命令或确认的时间少于处理命令的时间。 因此,带宽受到处理消息和发送另一个写请求的时间的限制

写入带宽 = 4 个字节(以 ns 为单位)

55.7.2.2 Write latency

延迟是发送写命令、处理命令和发送写确认所用的时间。

Serial Interprocessor Interface (SIPI)

56.1 Introduction

串行处理器间接口 (SIPI) 是在 LFAST(LVDS 快速异步串行传输)模块之上运行的应用层协议。 本地设备使用它来访问远程设备的共享内存。 SIPI 定义了两个设备之间的点对点全双工通信,其中 LFAST 用作两个设备之间通信的物理介质。

56.1.1可扩展性

SIPI 协议旨在使用少量互连信号在 2 个设备之间提供复杂的、高带宽、多主机、多通道内存接口。

但是该协议的设计方式可以实现协议的一个子集,其中芯片面积比功能更重要。

主要可扩展特性:

• 并发通道数:

• 全面实施 = 4

• 最低实施 = 1

• 完全实现有一个节点作为命令的发起者和目标。启动器或目标器的最低实现。

• 完全实现包括块传输功能,但此功能是可选的。

本节的其余部分描述了 SIPI 的完整实现,其中包括:

• 高级高性能总线 (AHB-Lite) 主接口

• 直接内存访问 (DMA) 接口

• LFAST Tx/Rx(发送/接收)接口以及外围总线接口 (IPS)

56.2 概述

SIPI 的一个实例可以充当发起者,或目标,或两者兼而有之。 SIPI 可以通过其 AHB 主接口或通过其 DMA 接口直接访问共享存储器。当节点充当发起者时使用 DMA 接口,而当节点充当目标时将使用 AHB 主接口。 SIPI 有四个通道,其中一个通道(通道 2)具有数据流功能。通道 0、1 和 3 的有效负载宽度为 32 位,通道 2 的数据宽度可以为 32 位,或在流式传输时为 256 位。根据 SIPI_CCRn 的设置,这些通道中的任何一个都可用于 DMA 访问或总线接口访问。 CRC 编码器计算命令帧上的 CRC。然后 SIPI 发起方在传输前将 CRC 附加到帧的末尾。

56.3 SIPI block diagram

56.4 Feature description

本节介绍 SIPI 模块的特性。

56.4.1 Main features

• 两个设备之间的点对点通信

• 全双工通信

• 四个通道,包括一个具有数据流功能的通道

• 每个通道的可配置 DMA 访问

• CRC 保护机制

• 超时保护机制

• 固定优先频道选择

• 流通道上的数据大小高达 256 位

• 用于为每个新传输分配顺序传输 ID 的公共标签池

• AHB 主接口,目标节点使用它来访问共享内存

• 目标节点包含一组九个 32 位内部寄存器来存储命令

• 发起方最多支持两个未完成的请求

56.4.2 Standard features

• IPS 总线接口 (PBRIDGE)

• SPP DMA2x 总线接口

• AHB 主接口

• LFAST Tx/Rx 接口

• 循环冗余校验错误检测 (CRC16)

56.5 SIPI operation from reset

当 SIPI 模块退出复位时,它可以运行并启用目标模式,无需配置控制寄存器。

56.6 Functional description

56.6.1 External signals

SIPI 没有芯片外部信号

56.6.2 Frame format

所有帧都具有相同的通用格式:

• 16 位标头

• 地址、地址和数据,或者什么都没有

• 16 位 CRC

有 2 个主要的命令组; 读和写。 这两组中有三种读/写格式:

• 32 位

• 16 位

• 8 位

每个命令生成三种不同响应之一:

• 读取数据

• 写确认

• 错误

还有一个额外的命令从 Target 节点请求模块 ID。 ID 是特定于特定设备的唯一 32 位 ID。 它通常与 JTAG ID 相同。 以下部分说明了用于实现所有命令和响应的四种不同帧格式。

帧数取决于数据缓冲区(与每个通道相关联),帧数据存储在发起方的数据缓冲区中。 地址和数据都以它们存储的相同顺序传输。

56.6.2.1 Register read request

56.6.2.2 Register read response, ID request response

56.6.2.3 Register write request

56.6.2.4 Trigger transfer, ID transfer, write acknowledge and streaming write acknowledge

56.6.2.5 Streaming write request

直接写操作用于设置流地址。

流式数据写入使用图 56-8 中所示的格式执行。

56.6.2.6 Header field

Header 字段包含 16 位的配置信息。 MSB 将首先发送。

56.6.2.6.1 SIPI header coding

图 56-9、表 56-1、图 56-10 和表 56-2 显示了 SIPI 报头比特是如何编码的。

表 56-1 显示了标头的位 [12:8] 的命令编码。

图 56-10 显示了标题中的通道号字段,表 56-2 显示了通道号编码。

56.6.2.7 Address field

地址字段为 32 位宽,首先发送 MSB。

56.6.2.8 Payload field

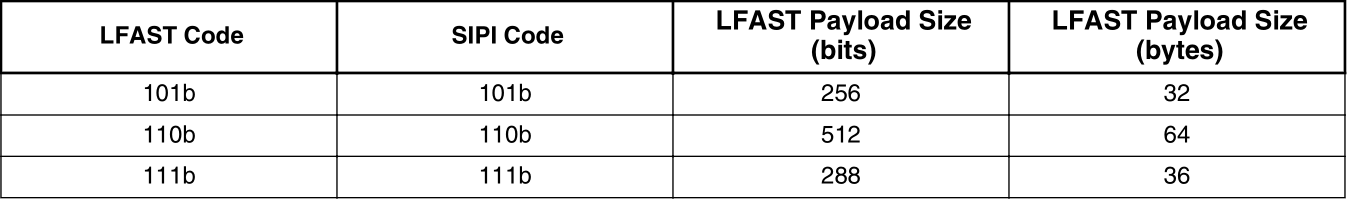

表 56-3 显示了 LFAST 帧的有效载荷大小。

表 56-4 显示了给定 SIPI 代码的 LFAST 转换编码.

1. SIPI 通道 0 在 LFAST 通道 A 上发送所有命令,在 LFAST 通道 A 上接收到的命令被处理,并在 LFAST 通道 A 上发回响应。

SIPI 通道 1 在 LFAST 通道 B 上发送所有命令,在 LFAST 通道 B 上接收到的命令被处理,并在 LFAST 通道 B 上发回响应。

SIPI 通道 2 在 LFAST 通道 C 上发送所有命令,在 LFAST 通道 C 上接收到的命令被处理,并在 LFAST 通道 C 上发回响应。

SIPI 通道 3 在 LFAST 通道 D 上发送所有命令,在 LFAST 通道 D 上接收到的命令被处理,并在 LFAST 通道 D 上发回响应。

56.6.2.9 CRC field

CRC 字段为 16 位宽,始终使用 CRC-16-CCITT 综合症 (x16 + x12 + x5 + 1) 启用计算。 MSB 在数据流中首先发送。

56.6.2.9.1 CRC field examples

56.6.2.9.1.1 Example 1 – 32 bit write on channel 1 with ID1

• Header = 260Ah

• Address = 1122_3344h

• Data = CCDD_EEFFh

• CRC = BF7Dh

56.6.2.9.1.2 Example 2 – 32 bit read on channel 2 with ID2

• Header = 420Ch

• Address = 89AB_CDEFh

• CRC = 6B80h

56.6.2.9.1.3 Example 3 – Event command on channel 3 with ID3

• Header = 6C0Eh

• CRC = B286h

56.7 Transfer types

本节介绍 SIPI 模块可用的传输类型。 SIPI 帧被插入到 LFAST 帧的有效载荷中,如以下示例中的图所示.

56.7.1 Read transfer

读取传输可以有两种类型:

• 读取请求传输(在发起节点)

• 读取响应传输(在目标节点)

56.7.1.1 Register read request transfer

如果有读请求传输,发起节点将发送标头、地址和 CRC 位,如图 56-11 所示。

56.7.2 Register read answer transfer

响应发起者节点的读请求,目标节点将发送header、payload和CRC16。 数据传输可以采用 8 位、16 位或 32 位模式(见图 56-12)。 在 8 位或 16 位模式的情况下,SIPI 数据的副本在有效载荷中发送(见图 56-13)。

• 对于 8 位传输,地址位 [31:2] 用作地址,位 [1:0] 用作字节使能。

• Bit[1:0]:

- 00 - 字节 3 启用 (MSB)

- 01 - 字节 2 已启用

- 10 - 字节 1 使能

- 11 - 字节 0 使能 (LSB)

• 对于16 位传输,地址位[31:1] 用作地址,位[0] 用作半字使能。

• Bit[0]:

- 0 - 启用半字 1 (MSB)

- 1 - 启用半字 0 (LSB)

56.7.3 Register Write transfer

寄存器写传输可以有两种类型:

• 正常写传输 - 通道 0、1、2 和 3

• 流式数据传输 - 仅限通道 2

如图 56-14 所示,可以通过通道 0、1、2 和 3 上的正常写传输来完成寄存器写传输(请参见正常写传输)。

56.7.3.1 Normal write transfer

正常的写传输包含标题、地址、数据(32 位)和 CRC,如图 56-15 所示。

• 对于 8 位传输,地址位 [31:2] 用作地址,位 [1:0] 用作字节使能。

• Bit1:0]:

• 00 - 字节 3 启用 (MSB)

• 01 - 字节 2 已启用

• 10 - 字节 1 使能

• 11 - 字节 0 使能 (LSB)

• 对于 16 位传输,地址位 [31:1] 用作地址,位 [0] 用作半字使能。

• Bit[0]:

• 0 - 启用半字 1 (MSB)

• 1 - 启用半字 0 (LSB)

56.7.3.2 Streaming write transfer

流式写入传输具有 256 位的有效负载。

56.7.3.2.1 Streaming write transfer with address

使用直接写传输来设置地址。 SIPI 最大计数寄存器 (SIPI_MAXCR) 和 SIPI 地址重载寄存器 (SIPI_ARR) 在 SIPI 地址计数寄存器 (SIPI_ACR) 之前写入。 这是为了避免 SIPI 尝试访问非共享内存的不良行为。 这仅适用于第一个流命令,后续流命令可能不需要写入 SIPI_MAXCR 和 SIPI_ARR(参见 SIPI 最大计数寄存器 (SIPI_MAXCR)、SIPI 地址计数寄存器 (SIPI_ACR) 和 SIPI 地址重载寄存器 (SIPI_ARR) ))。

56.7.3.2.2 Streaming transfer with data

图 56-16 显示了包含数据的流传输的数据包结构。

56.7.4 Write Acknowledge transfer

写确认传输仅包含标头和 CRC 位(请参阅写确认传输。CRC 位是在标头字段上计算的。

56.7.5 ID request response

56.7.5.1 ID request transfer

如图 56-18 所示,发起节点发送一个 ID 请求。

ID 请求响应包含 CHIP ID 的值而不是数据。

56.8 Transfer API and flow charts

执行以下步骤以生成单个写传输请求(图 56-20):

-

在发起节点配置数据和SIPI_CCRn。

-

在发起节点配置SIPI_CARn。

一旦写入通道地址寄存器 (SIPI_CARn) 并且如果 CCRn[CHEN] = 1,发起方 SIPI 将计算头、地址和数据字段的 CRC,并开始向 LFAST 传输数据。

-

软件轮询状态寄存器位(SIPI_CSRn)以确定请求何时完成,SIPI_CSRn[ACKR] = 1。如果相应的 SIPI_CIRn[ACKIE] = 1,将产生中断。

在单个写入传输请求接收中(图 56-21):

4. 目标节点将地址、数据和控制信息放在其 AHB 主接口上。

5. 当该过程完成后,目标节点将生成一个确认帧并将其发送回LFAST。

对于多写传输请求生成(图 56-22):

- 软件将配置 DMA 的传输控制描述符 (TCD)。

- 软件将写入 SIPI_CCRn[CHEN] = 1 和 SIPI_CCRn[DAN] = 1。

- SIPI 将开始通过其 DMA 接口将数据复制到 SIPI_CDRn,具体取决于传输计数和数据寄存器大小。 SIPI_CDR2_0 应与 MSB 一起写入。

- 复制过程完成后,发起方SIPI 将计算头、地址和数据字段的CRC,并开始向LFAST 传输数据。

- 软件应轮询 SIPI_CSRn 状态寄存器位以确定请求是否已完成。 如果 SIPI_CSRn[ACKR] = 1,将产生中断(如果对应的 SIPI_CIRn[ACKIE] = 1)。

- 如果 SIPI_CCRn[DEN] = 1,SIPI 请求将传输到 DMA 控制器。 如果不是,则状态机进入空闲状态。

- 将重复步骤 4-7。

在多次写入传输请求接收时(图 56-22):

- 目标节点将地址、数据和控制信息放在其 AHB 主接口上。

- 当该过程完成后,目标节点将生成一个确认帧并将其发送回LFAST。

对于生成单次读取传输请求(图 56-23): - Software/DMA会配置SIPI_CCRn和SIPI_CDRn,最后一步是写CARn。

- 一旦写入 SIPI_CAR,发起方 SIPI 将计算头部和地址字段的 CRC,并开始向 LFAST 传输数据。

- 软件应轮询 CSRn 以确定请求何时完成。 如果 SIPI_CSRn[RAR] = 1,将产生中断(如果 SIPI_CIRn[RAIE] = 1)。 如果 SIPI_CSRn[RAR] 未设置,则 SIPI_ERR[TOEn] = 1,表示发生超时。

- 如果 SIPI_CSRn[RAR] = 1,则软件可以读取数据寄存器,如果 SIPI_CSRn[RAR] = 0,则可以进行其他必要的操作。

在接收到 Single Read 传输请求时(图 56-23):

- 目标节点将地址和控制信息放在其 AHB 主接口上。

- 进程完成后,目标节点将读取响应发送回LFAST。

对于多读传输请求生成(图 56-24): - Software/DMA会配置SIPI_CCRn和SIPI_CDRn,最后一步是写SIPI_CARn。

- 写入通道地址寄存器后,发起方 SIPI 将计算头部和地址字段的 CRC,然后开始向 LFAST 传输数据。

- 软件应轮询 SIPI_CSRn 以确定请求何时完成。 如果 SIPI_CSRn[RAR] = 1 且 SIPI_CIRn[RAIE] = 1,将产生中断。 如果 SIPI_CSRn[RAR] 未设置,则 SIPI_ERR[TOEn] = 1,表示超时。

- 对于多个请求,将重复步骤 2-3。

在多次读取传输请求接收时(图 56-24):

- 然后目标节点将开始通过其 AHB 接口读取数据。

- 当传输完成/所有数据寄存器已满时,它会计算CRC并将响应帧发送回LFAST。

注意:

在 DMA 传输中,硬件也会清除读取应答中断引脚。 这可能会导致软件陷入麻烦,因为它通过不断计算接收和清除中断的次数来跟踪请求。

图 56-25、图 56-26、图 56-27 和图 56-28 显示了数据的 SIPI 数据流。

56.9 DMA programming sequence

DMA 编程顺序如下:

- 软件配置 TCD(DMA 数据)。

- DMA 从 RAM 传输到 SIPI 寄存器。

- SIPI 开始通过 LFAST Tx 端口传输数据。

- 如果收到确认或故障响应,SIPI 将重复该过程。 如果收到任何错误响应,SIPI 将进入空闲状态。 中断将由 SIPI 标记,软件将控制 SIPI。

- 当 SIPI 接收到读响应并且 LFAST 的错误标志没有被置位时,它会发起一个 DMA 请求。 如果 LFAST 断言错误标志,则 SIPI 移至步骤 8。

- 当SIPI发起DMA请求时,DMA在SIPI和RAM之间传输数据。

- 如果DMA传输小循环/主循环完成,并且请求被否定,则ipd_request被否定。

- 如果发生错误:

• SIPI 产生中断

• 软件控制 SIPI - 重复步骤 5 – 8,直到传输完成。

56.10 Modes of operation

SIPI 具有三种运行模式:

• 初始化

• 普通的

• 模块禁用

硬件复位后,SIPI 处于模块禁用模式,这有助于降低功耗。

56.10.1 Initialization mode

要进入初始化模式,软件写入 SIPI_MCR[INIT]=1 必须在尝试写入 SIPI_MCR[INIT] 之前设置 SIPI_MCR[MOEN]。 要退出初始化模式,软件写入 SIPI_MCR[INIT]=0(参见 SIPI 模块配置寄存器 (SIPI_MCR))。

注意:

建议软件在设置 SIPI_MCR[INIT] 之前检查 SIPI (SIPI_MCR[MOEN]) 的状态。

56.10.2 Normal mode

一旦软件完成了 SIPI 的初始化(SIPI_MCR[INIT]=1),它可以通过写入 SIPI_MCR[INIT]=0 进入正常模式。 对于所有数据传输,SIPI 需要处于正常模式(请参阅 SIPI 模块配置寄存器 (SIPI_MCR))。

注意:

在尝试写入 SIPI_MCR[INIT] (SIPI_MCR[MOEN]=1) 之前,必须启用 SIPI。

56.10.3 Module Disable (MD)

SIPI 中的 MD 模式用于帮助降低功耗。 默认情况下,SIPI 处于禁用模式,SIPI_MCR[MOEN]=0,并通过写入 SIPI_MCR[MOEN]=1 退出(参见 SIPI 模块配置寄存器 (SIPI_MCR))。 未来的 SIPI Tx 传输在模块禁用模式下被禁用。 要禁用 Rx 功能,必须取消目标启用 (TEN) 位字段,然后内部 Rx 状态机重置为初始状态。

56.11 Errors

本节介绍在 SIPI 操作期间可能发生的潜在错误。

56.11.1 Timeout error

当在相应 CTORn[TOR] 字段设置中配置的时间内未收到确认/响应时,在发起方节点生成超时错误

(请参阅 SIPI 通道超时寄存器 0 (SIPI_CTOR0)、SIPI 通道超时寄存器 1 (SIPI_CTOR1), SIPI 通道超时寄存器 2 (SIPI_CTOR2) 和 SIPI 通道超时寄存器 3 (SIPI_CTOR3))。 当 ERR[TOEn]=1 时指示超时错误(参见 SIPI 错误寄存器 (SIPI_ERR))。

注意:

即使发生超时,SIPI 也不应丢弃响应。

软件将在传输后轮询错误和状态标志,以查看是否存在超时错误。 如果存在超时错误,则可以丢弃收到的响应。

56.11.2 CRC error

当与帧一起接收的 CRC 与计算的 CRC 不匹配时,目标节点会生成 CRC 错误,并且设置了 SR[GCRCE](参见 SIPI 状态寄存器 (SIPI_SR))。 如果 MCR[CRCIE]=1(参见 SIPI 模块配置寄存器 (SIPI_MCR)),则将发出中断。

注意:

生成 CRC 错误时,目标节点不会向发起节点发送确认。 如果设置了相应的中断使能位,将在目标端产生一个中断。 发起方节点将检测到超时并采取必要的措施。

56.11.3 Maximum count reached error

达到最大计数错误仅在目标节点处生成。 它在 SIPI_ACR 的值等于 SIPI_MAXCR 时生成(参见 SIPI 最大计数寄存器 (SIPI_MAXCR) 和 SIPI 地址计数寄存器 (SIPI_ACR))。 当达到最大计数时,SIPI_SR[MCR] = 1(参见 SIPI 状态寄存器 (SIPI_SR))。 如果 SIPI_MCR[MCRIE] = 1,将产生中断(参见 SIPI 模块配置寄存器 (SIPI_MCR))。

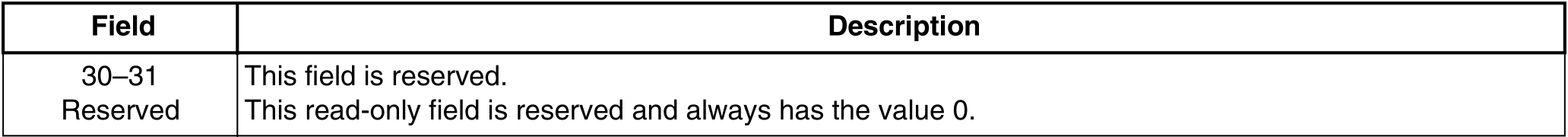

56.11.4 Transaction ID error

事务 ID (TID) 错误始终仅在发起方节点生成。 当标头位 15–13 不匹配 SIPI_CSRn[TID](事务 ID 位,请参见 SIPI 通道状态寄存器 0 (SIPI_CSR0)、SIPI 通道状态寄存器 1 (SIPI_CSR1)、SIPI 通道状态寄存器 2 (SIPI_CSR2) 和 SIPI 通道状态寄存器 3 (SIPI_CSR3))。 当检测到 TID 错误时 SIPI_CSRn[TIDE] = 1,如果 SIPI_CIRn[TIDIE] = 1 将产生中断(参见 SIPI 通道中断寄存器 0 (SIPI_CIR0)、SIPI 通道中断寄存器 1 (SIPI_CIR1)、SIPI 通道中断寄存器 2 (SIPI_CIR2) 和 SIPI 通道中断寄存器 3 (SIPI_CIR3))。

56.11.5 Acknowledge error

仅从发起方收到不正确的确认。 当收到的确认不正确时,将设置 SIPI_ERR[ACKRn](参见 SIPI 错误寄存器 (SIPI_ERR))。 如果 SIPI_CIRn[WAIE]=1,将产生中断(参见 SIPI 通道中断寄存器 0 (SIPI_CIR0)、SIPI 通道中断寄存器 1 (SIPI_CIR1)、SIPI 通道中断寄存器 2 (SIPI_CIR2) 和 SIPI 通道中断寄存器 3 (SIPI_CIR3) )。

56.12 CRC calculation

示例:如果标题为 AABBh,地址为 1122_3344h,数据为 CCDD_EEFFh。 然后CRC计算将如下进行:

- CRC 种子由 FFFF_FFFFh 初始化。

2)所有数据在发送到CRC引擎之前都会被镜像(例如,MSB将作为LSB发送)。 - 所以报头将作为 DD55_0000h 发送。

- 地址将作为 22CC_4488h 发送。

- 数据将作为 FF77_BB33h 发送。

56.13 Interrupt logic

中断逻辑的描述可以在下图中找到。

56.14 SIPI control and status overview

下图显示了传输与 SIPI 控制和状态寄存器之间的关系。

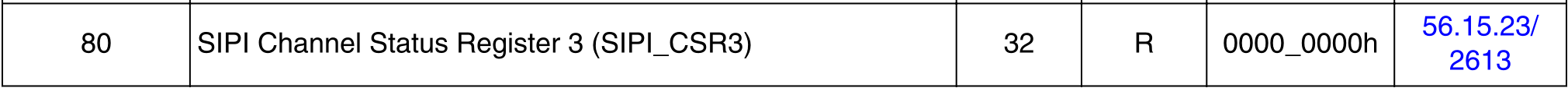

56.15 Memory map and register definition

56.15.1 SIPI Channel Control Register 0 (SIPI_CCR0)

注意:

单个通道上不支持背靠背事务(例如,如果通道忙位 SIPI_CSR0[CB] = 1 配置为通道,则在数据缓冲区为空且通道是免费的,SIPI_CSR0[CB] = 0)。

优先级调度:首先写入 SIPI_CARn 的通道将首先获得访问权限,而不管其在传输开始时的优先级。随着请求更多传输,将根据优先级方案解决优先级(例如,通道 0 – 通道 1 – 通道 2 – 通道 3)。

每次 LFAST 未准备好接收数据并且没有通道等待数据传输时,都会进行调度。

调度的原因是所有通道共享一个公共CRC模块。如果 LFAST 在整个过程中准备好接收数据,它只会在开始时发生,稍后将根据优先级方案解决优先级。

注意:

该寄存器仅在初始化模式 (SIPI_MCR[INIT] = 1) 下可写,命令位除外(例如,TC、WL、ST、IDT、RRT 和 WRT)。此外,仅当相应的通道忙位未置位时才能写入命令位(SIPI_CSRn[CB] = 1(参见 SIPI 通道状态寄存器 0 (SIPI_CSR0))。软件将需要先轮询相应的通道忙位,然后再尝试更改命令类型。

一次只能传输一个通道。因此,只有一个频道可以保持忙碌状态。允许传输完整命令的最长时间为 9 个时钟周期。频道的命令类型只有在它不再忙时才能更改。此外,要发送命令,我们需要写入相应的 SIPI_CARn(参见 SIPI 通道地址寄存器 0 (SIPI_CAR0))。

56.15.2 SIPI Channel Status Register 0 (SIPI_CSR0)

CSR0 包含当前传输的状态位。

56.15.3 SIPI Channel Interrupt Register 0 (SIPI_CIR0)

SIPI_CIR0 包含通道 0 的中断使能位。

Chapter 57 LVDS Fast Asynchronous Serial Transmission (LFAST) – Interprocessor Communications

57.1 Introduction

本章介绍 LFAST 模块的规格,该模块实现了 LVDS 快速异步串行传输 (LFAST) 模块。 LFAST 用于处理器间通信的双模式(软件可配置的主/从操作)。

57.2 Block diagram

下图描述了 LFAST 与设备上其他模块的交互。

57.3 External signals

LFAST 是一个带有以下信号的五针接口:

• lfast_sysclk

• LFAST 主机和从机的参考时钟

• txdatap/txdatan

• 差分传输 (Tx) 接口对

• rxdatap/rxdatan

• 差分接收 (Rx) 接口对

LFAST 接口是一个异步高速 LVDS 接口。

57.3.1 LFAST operating data rates

LFAST 主机通过向 LFAST 从机发出适当的接口控制逻辑通道 (ICLC) 数据包来控制数据速率的变化。 此后,数据速率 6.5 Mbps/5 Mbps(lfast_sysclk ÷ 4 或 lfast_sysclk ÷ 2)被称为低数据速率,高数据速率在数据手册中。

57.4 LFAST frame structure

LFAST 帧由三个字段组成:

• 同步模式

• 标题

• 有效载荷

同步模式和标头字段是固定长度的。

同步模式用于同步 LFAST 模块中的传入数据流。

帧的报头字段区分各种类型的数据和传输的控制,还包含有关有效载荷长度的信息。 有效负载字段是通过通道传输的实际数据。 有关 LFAST 帧的详细信息,请参见图 57-2。

相同的协议用于数据、控制和状态信息的传输和接收接口。 同步模式(16 位)和标头(8 位)存在于每一帧中。

帧结构如图 57-3 所示,由以下部分组成:

• 16 位同步模式:用于时钟同步和模式识别。 每帧开始的帧同步码是唯一的保留字,用于识别接收到的数据是否是帧的开始,并用于与流数据同步(时钟相位提取)。 同步序列用于提供高质量的自相关。 LFAST 16 位同步序列 = 1010_1000_0100_1011b = A84Bh。

• Header - 3 MSB (b7 - b5):定义有效载荷大小,如表 57-1 所示:

• Header - (b4 - b1):定义逻辑信道类型,指示帧承载的有效负载类型。 帧的有效载荷字段如何用于任何其他逻辑信道类型是系统侧模块特定的,除了接口控制逻辑信道类型和清除发送 (CTS) 帧的情况。

• 标头- (b0):LFAST 主设备和从设备上的CTS。

• 有效负载:取决于帧类型的内容。

• 逐帧位:该位决定进入休眠模式(1 = 休眠模式,0 = 正常模式)

57.5 Features

• 支持双模式(寄存器可配置主/从)。

• 支持异步数据传输,最高可达产品数据表中显示的最大数据速率。

• 发送和接收数据、CTS、ICLC 和未经请求的帧。

• 接收 ICLC 帧

• 为Tx 和Rx 通道提供五个中断。

• 支持处理器控制的 8 位有效载荷大小的 ICLC 帧传输,以实现数据速率变化和测试模式。

• 支持LFAST 定义的CTS 控制数据传输。除非启用 CTS 模式,否则数据传输和接收之间没有依赖性。

• 支持使用滑动窗口协议的流量控制。

• 为具有 32、64、96、128、256 或 288 位可变有效载荷大小的数据帧提供可配置的帧长度。

• 提供有效载荷大小为 96 位的数据帧长度的发送和有效载荷大小为 128 位的数据帧的接收。

• 为具有8、32、64、96、128、256 或288 位可变有效载荷大小的未经请求的帧提供可配置的帧长度。

• 通过寄存器支持PLL 配置(例如,反馈环路分频器等)。

• 通过寄存器支持LVDS 配置。

• 支持多种环回方式检查物理接口。

• 支持在从模式下自动生成 ping 响应。

• 支持检测不支持的频道号和不支持的有效载荷大小。

57.6 Memory map and register definition

所有寄存器均为 32 位宽。

注意:

对所有未实现寄存器的读/写访问和对只读寄存器的写访问将返回传输错误。

57.6.1 LFAST Mode Configuration Register (LFAST_MCR)

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)