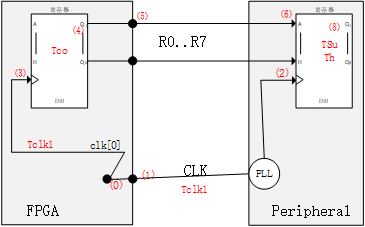

一、参考模型

- 图源来自《【抢先版】小梅哥FPGA时序约束从遥望到领悟》

二、参数分析

- T(0)->(3) = Tclk1

- T(3)->(4) = Tco

- T(4)->(5) + T(5)->(6) = Tdata

- T(4)->(5) = Tdata(Init)

- T(5)->(6) = Tdata(Pcb)

- T(5)->(6)

- T(0)->(1) + T(1)->(7) = Tclk2

- T(0)->(1) = Tclk2(Init)

- T(1)->(7) = Tclk2(Pcb)

(4)->(5)的走线是在FPGA芯片内部(IC)

(5)->(6)的走线是在PCB板上

(0)->(1)的走线是在FPGA芯片内部(IC)

(1)->(7)的走线是在PCB板上

计算PCB板上电信号的传输时间,可以将电信号等效为光速,得到的电信号传输时间与长度关系的参数为5555mil/ns

1mil = 0.0254mm

5555mil/na -> 141.097mm/ns

三、建立时间余量分析 Slack(Tsu)

- Data Require Time(数据要求时间) = Tclk2 - Tsu(芯片数据建立时间) + Latch edge(接收沿) = Tclk2(Init) + Tclk2(Pcb) - Tsu + Latch edge(接收沿)

- Data Arrival Time(数据到达时间) = Tclk1 + Tco + Tdata + Launch edge(发送沿) = Tclk1 + Tco + Tdata(Init) + Tdata(Pcb) + Launch edge(发送沿)

- Latch edge(接收沿) - Launch edge(发送沿) = Tclk(因为是一个时钟,所以相减就是时钟周期)

- Slack(Tsu)

- Data Require Time - Data Arrival Time = (Tclk2 - Tsu + Latch edge) - (Tclk1 + Tco + Tdata + Launch edge)

- Data Require Time - Data Arrival Time = (Tclk2(Init) + Tclk2(Pcb) - Tsu + Latch edge) - (Tclk1 + Tco + Tdata(Init) + Tdata(Pcb) + Launch edge)

- Data Require Time - Data Arrival Time = (Tclk2(Init) + Tclk2(Pcb) - Tsu) - (Tclk1 + Tco + Tdata(Init) + Tdata(Pcb)) + Tclk

- Data Require Time - Data Arrival Time >= 0

- Tclk2(Init) - Tclk1 -Tco - Tdata(Init) >= -Tclk2(Pcb) + Tsu +Tdata(Pcb) - Tclk (注:左边是未知量,右边是可知量)

- Tclk2(Init) - Tclk1 -Tco - Tdata(Init) + Tclk >= -Tclk2(Pcb) + Tsu +Tdata(Pcb)

- -Tclk2(Pcb) + Tsu +Tdata(Pcb)就是最大传输延迟:output delay max = Tdata(pcb) - Tclk2(pcb) + Tsu

四、保持时间余量分析 Slack(Th)

- Data Require Time(数据要求时间) = Tclk2 + Th(芯片数据保持时间) + Latch edge(接收沿) = Tclk2(Init) + Tclk2(Pcb) + Th + Latch edge(接收沿)

- Data Arrival Time(数据到达时间) = Tclk1 + Tco + Tdata + Launch edge(发送沿) = Tclk1 + Tco + Tdata(Init) + Tdata(Pcb) + Launch edge(发送沿)

- Slack(Th)

- Data Arrival Time(数据到达时间) - Data Require Time(数据要求时间)

- 同样的,可以算出,最小输出延迟

- Output delay min = Tdata(pcb) - Tclk2(pcb) - Th

五、综上所述

- output delay max = Tdata(pcb) - Tclk2(pcb) + Tsu

- Output delay min = Tdata(pcb) - Tclk2(pcb) - Th

如果,PCB板上的数据走线长度与时钟走线长度一样,即:(5)->(6) = (1)->(7)

那么,Tdata(pcb) = Tclk2(pcb)

- output delay max = Tsu

- Output delay min = -Th

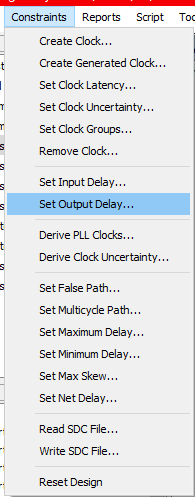

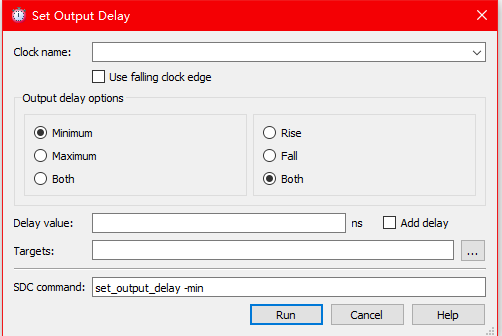

六、步骤

-

设计时钟约束

-

设计输出延迟

最大延迟

最小延迟

七、时钟与数据反向输出

Tsu

- Data Require Time = Tclk2(Int) - Tsu + Latch Edge

- Data Arrival Time = Tclk1(Pcb) + Tclk1(Int) + Tco + Tdata(Pcb) + Tdata(Int) + Lanch Edge

- Slack(Tsu) = Data Require Time - Data Arrival Time

- Slack(Tsu) = (Tclk2(Int) - Tsu + Latch Edge) - (Tclk1(Pcb) + Tclk1(Int) + Tco + Tdata(Pcb) + Tdata(Int) + Lanch Edge) >= 0

- Tclk2(Int) - Tclk1(Int) -Tco - Tdata(Int) >= (Lanch Edge - Latch Edge) + Tsu + Tclk1(Pcb) + Tdata(Pcb)

- output delay max = Tclk1(Pcb) - Tdata(Pcb) + Tsu

Th

- Data Require Time = Tclk2(Int) + Th + Latch Edge

- Data Arrival Time = Tclk1(Pcb) + Tclk1(Int) + Tco + Tdata(Pcb) + Tdata(Int) + Lanch Edge

- Slack(Th) = Data Arrival Time - Data Require Time

- Slack(Th) = (Tclk1(Pcb) + Tclk1(Int) + Tco + Tdata(Pcb) + Tdata(Int) + Lanch Edge) - (Tclk2(Int) + Th + Latch Edge) >= 0

- (Lanch Edge - Latch Edge) + Tclk1(Pcb) + Tdata(Pcb) - Th >= -Tclk1(Int) - Tco - Tdata(Int) + Tclk2(Int)

- output delay min = Tclk1(Pcb) + Tdata(Pcb) - Th

八、IO输出通用约束模型分析

Tskew = Tclk2 - Tclk1

Tskew(Pcb) = Tclk2(Pcb) - Tclk1(Pcb)

时钟与数据同向时

Tclk1(Pcb) = 0

- output delay max = Tdata(pcb) - Tclk2(pcb) + Tsu = Tdata(pcb) - (Tclk2(pcb) - Tclk1(Pcb)) + Tsu = Tdata(pcb) - Tskew(Pcb) + Tsu

- output delay min = Tdata(pcb) - Tclk2(pcb) - Th = Tdata(pcb) - (Tclk2(pcb) - Tclk1(Pcb)) - Th = Tdata(pcb) - Tskew(Pcb) - Th

时钟与数据反向时

Tclk2(Pcb) = 0

- output delay max = Tdata(Pcb) + Tclk1(Pcb) + Tsu = Tdata(Pcb) - (Tclk2(Pcb) - Tclk1(Pcb)) + Tsu = Tdata(pcb) - Tskew(Pcb) + Tsu

- output delay min = Tdata(Pcb) + Tclk1(Pcb) - Th = Tdata(Pcb) -(Tclk2(Pcb) - Tclk1(Pcb)) - Th = Tdata(pcb) - Tskew(Pcb) - Th

综上,IO输出约束通用公式为

- output delay max = Tdata(pcb) - Tskew(Pcb) + Tsu

- output delay min = data(pcb) - Tskew(Pcb) - Th