刚接触Altera FPGA,测试时程序时,未使用的管脚有输出,如没有驱动的LED点亮了,这是因为

未使用的管脚系统默认设置为驱动接地,低电平驱动的LED就点亮了,本文将说明如何修改未使用管脚系统默认的设置。

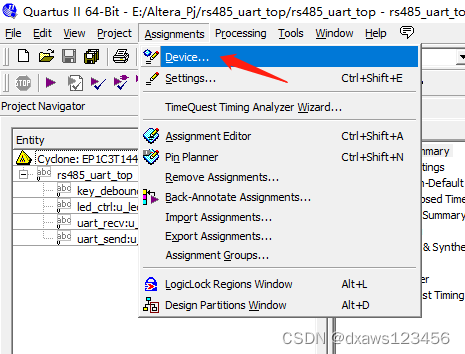

步骤1:如下图,进入Device...

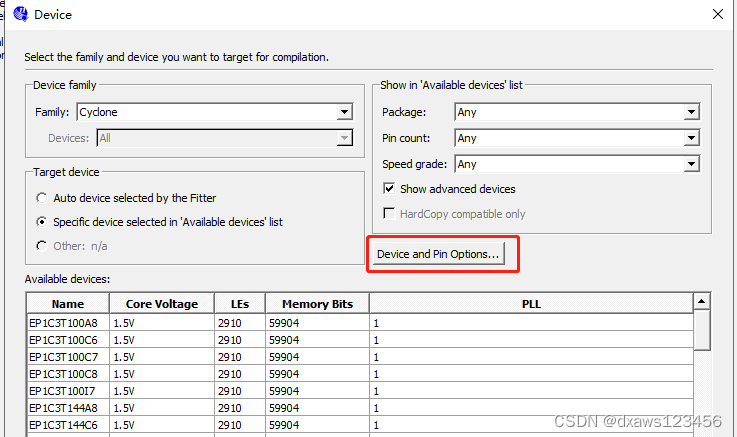

步骤2:弹出下图窗口,然后点击红框处。

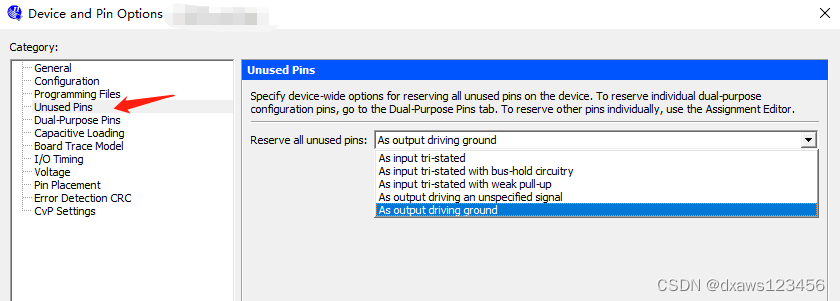

步骤3:弹出下图窗口,然后选择(红色箭头处),右边出现未使用管脚默认设置。

步骤4:选择你需要的默认设置。

未使用管脚默认设置解释:

As output driving ground 作为输出驱动地

As input tri-stated 作为三态输入

As input tri-stated with bus-hold circuitry 作为带总线保持电路的三态输入

As input tri-stated with weak pull-up 作为具有弱上拉的三态输入

As output driving an unspecified signal 作为未指定信号的驱动输出

本文到此完,看到请点赞+评论!!

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)