2022芯原设计笔试题分析和讨论

以下仅为个人理解和分析,不保证正确,欢迎大家发表自己的想法,讨论出正确答案!

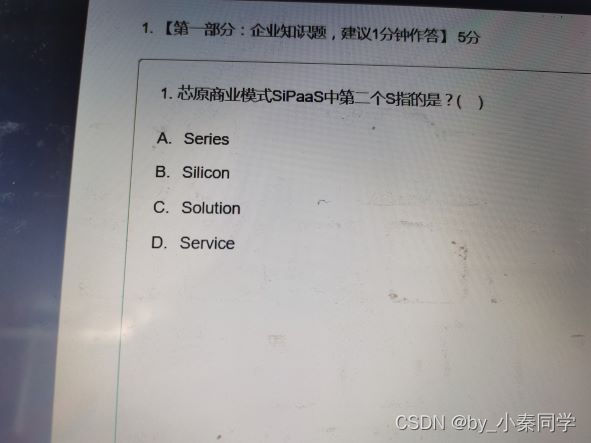

企业知识题

1.1 D

芯原的主要经营模式为芯片设计平台即服务(Silicon Platform as a Service,SiPaaS)模式。

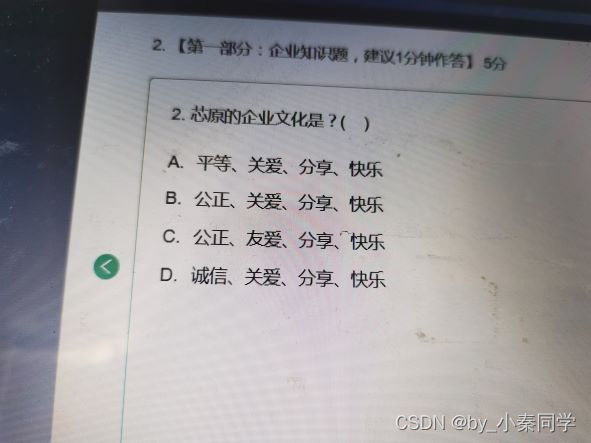

1.2 B

公司遵循“Fair(公平)、Care(关爱)、Share(共享)、Cheer(快乐)”的企业文化

智力题

2.1 C

这个题比较简单,中间的数字是前后两个字母之间间隔字母的个数(字母歌大家都会唱吧?)再加一。如:R-T,中间含有1个S,所以就是2.

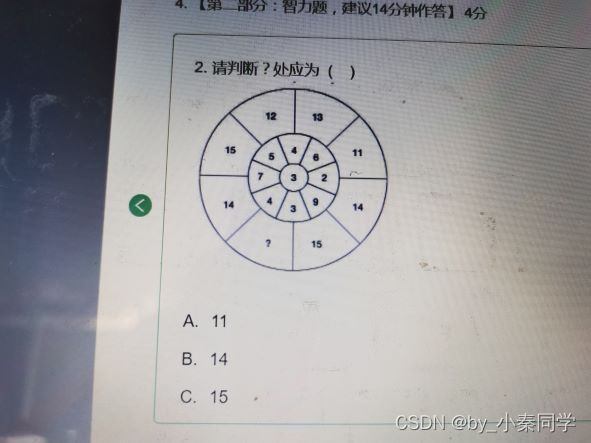

2.2 D

外圈等于相邻内圈扇形和再加上圆心的3,例如13=4+6+3;

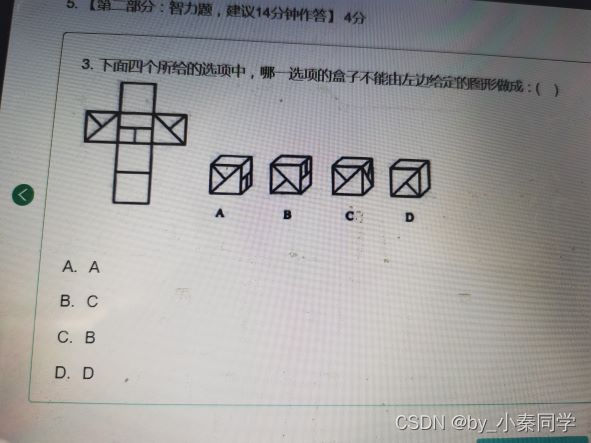

2.3 C

注意题目是不能由左边给定的图形做成,是不能

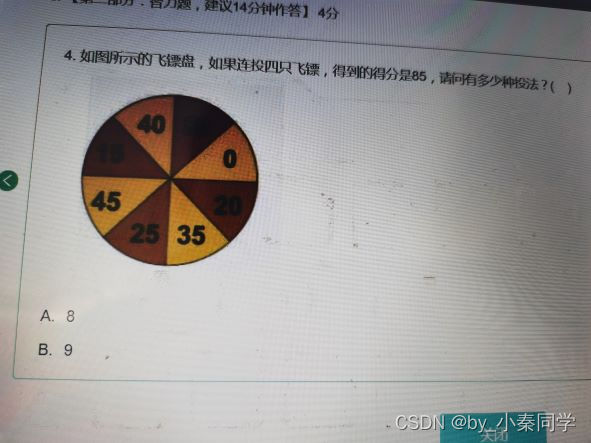

2.4 未知

看不清图中的值

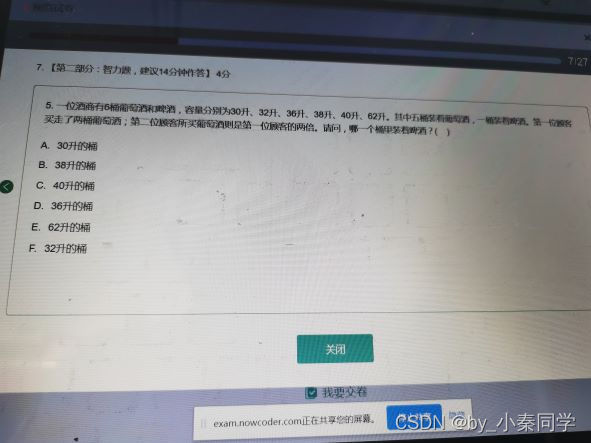

2.5 C

6桶酒加起来后的和减去啤酒的容量,是3的倍数即可

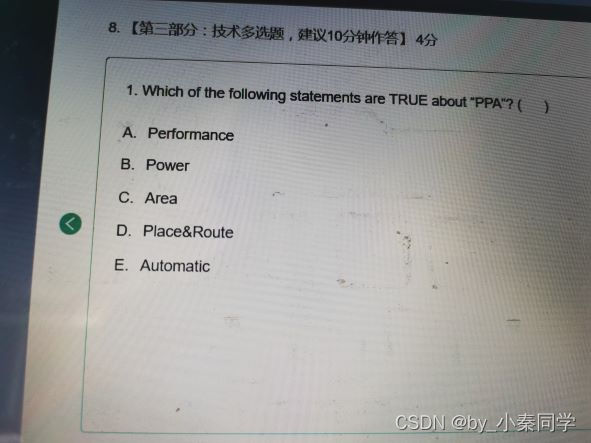

技术多选题

3.1 A、B、C

PPA是指性能、功耗和面积

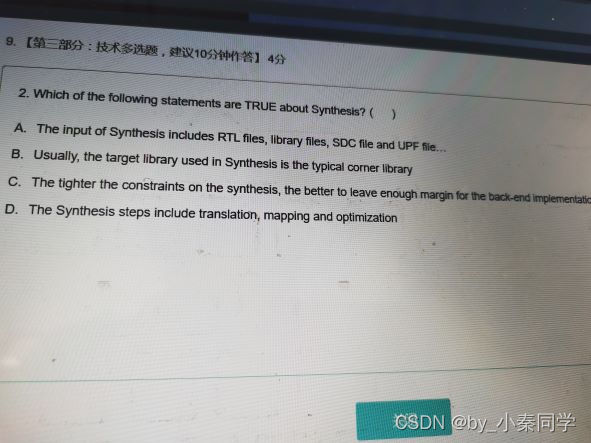

3.2 BD

不是很确定这个答案,C的约束设置不能过于严格,在优化时可能会得不到结果;B感觉是对的,A中的sdc文件是综合后生成的,D正确

A:综合需要的文件:RTL文件、标准单元的库文件、其他库文件。

D:综合主要包括三个阶段:转换(translation)、优化 (optimization)与映射(mapping)。

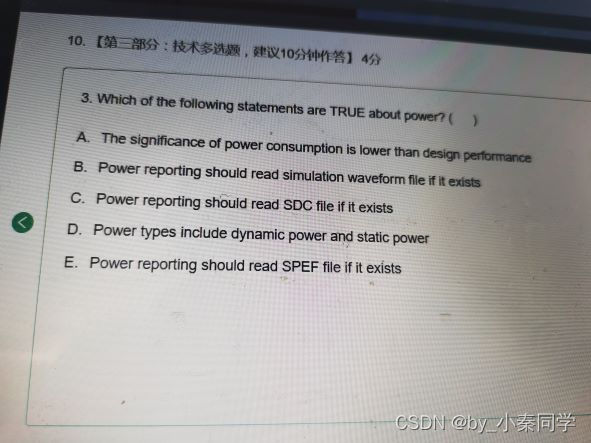

3.3 ADE

A:功耗和性能的关系需要具体情况具体分析,不能直接说功耗的重要性不如性能

D:功耗分为动态功耗和静态功耗

B:功耗分析和仿真应该没什么关系

C:SDC文件是标准延时约束文件,个人感觉也没啥关系

E:SPEF是Standard Parasitic Extraction Format的缩写,用于描述芯片在PR之后实际电路中的 R L C 的值。由于芯片的 current loops非常窄也比较短,所以一般不考虑芯片的电感,所以通常SPEF中包含的寄生参数为RC值。

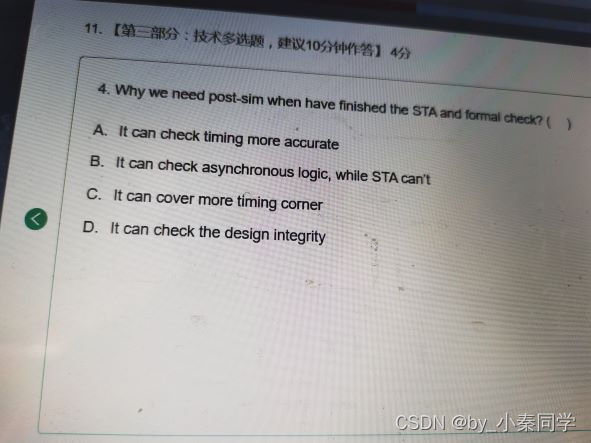

3.4 ABD

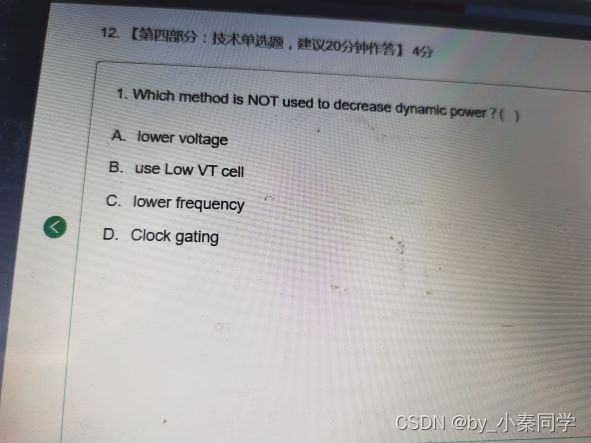

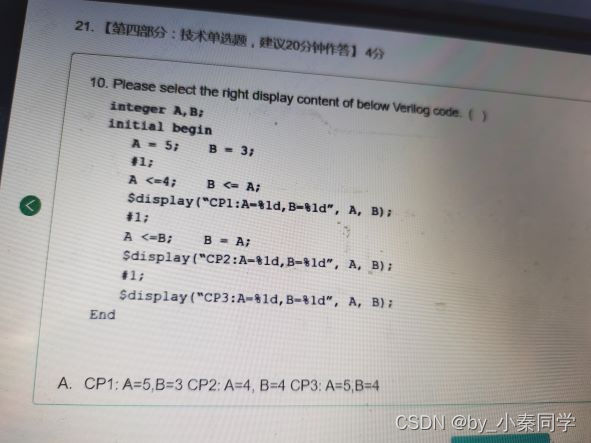

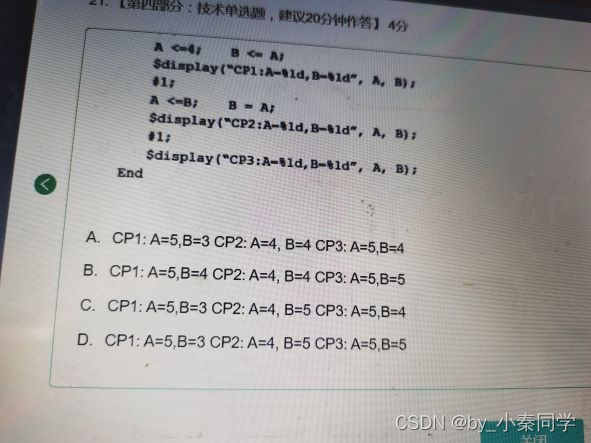

技术单选题

4.1 B

low VT会增加性能,但是同时也会增加漏电流,错误

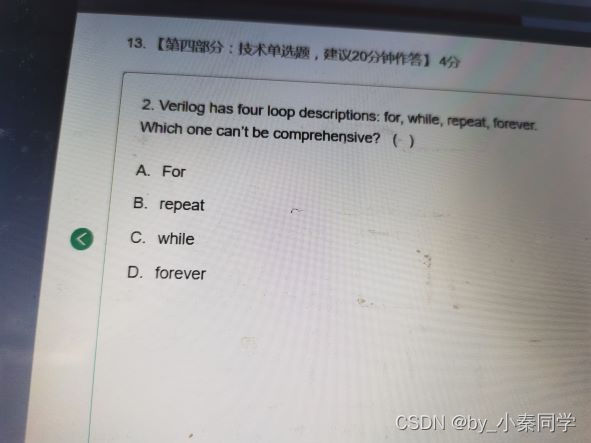

4.2 D

forever不能实现,verilog中的循环语句的循环次数必须有限,因为verilog最终都是转换成硬件电路的,无限的循环次数是无法转换的。

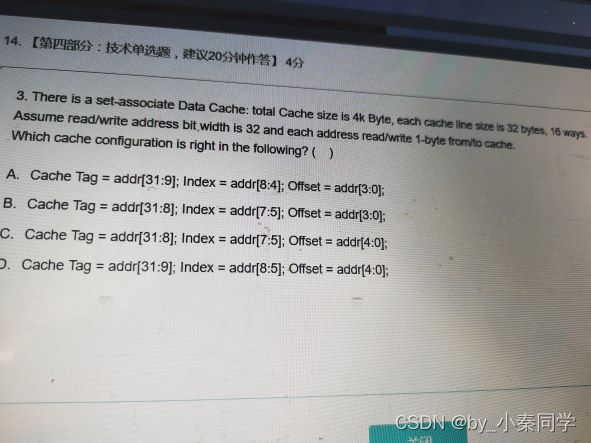

4.3 D

index表示的是多路组相连cache结构的路数,这里就是16,需要4位;offset表示的是单个cache中的1byte位置,这里是32,需要5位,所以答案是D;tag用来在使用index选出cache位于哪一组后去比较具体的cache块位于哪一路(没太明白)。

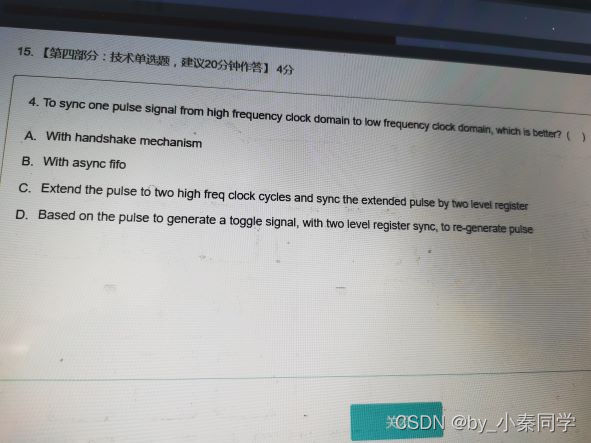

4.4 A

这个题目问的是一个脉冲信号,从快时钟域同步到慢时钟域时,哪个方法最好;A是握手,B是异步FIFO,C是在快时钟域将信号延长至两个快时钟周期,然后两级打拍,D我没明白(o(╥﹏╥)o)

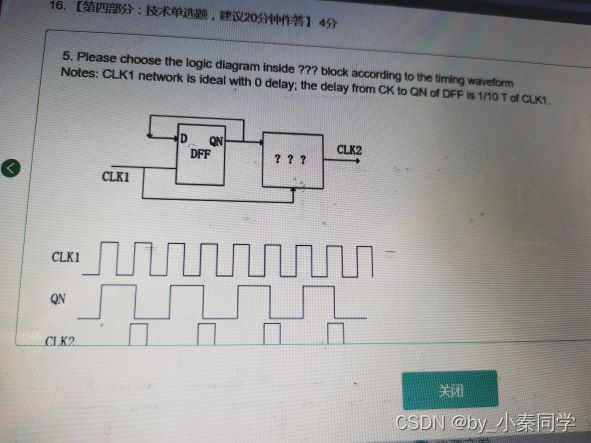

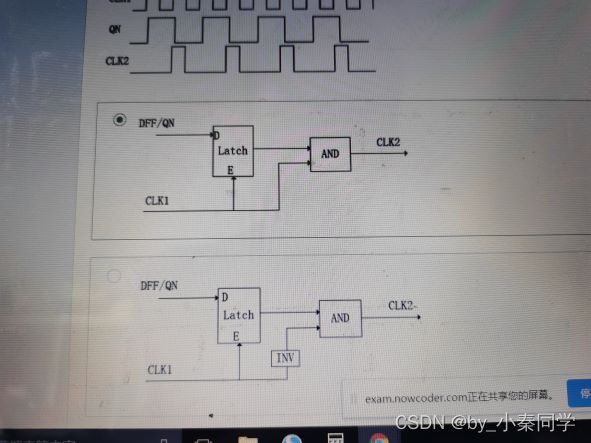

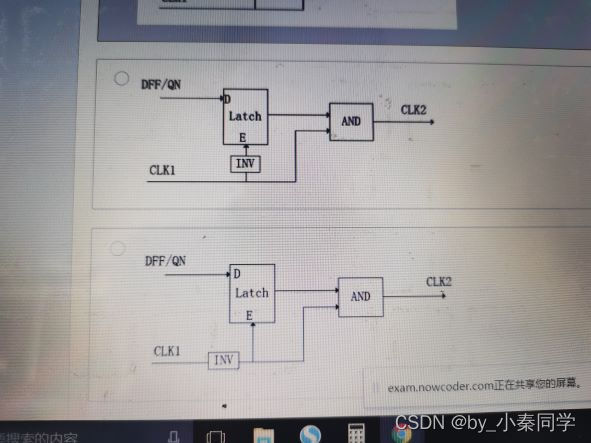

4.5 C

先不考虑DFF的输出延时,可以得到CLK的数据是CLK1和QN非的与门得到的结果,那就要考虑如何把DFF的输出延时的影响去掉;参考选项,选项中都是用的锁存器,根据非门,首先排除A和D,然后B中得到的CLK2和CLK1的高电平对应不上,所以就是C。

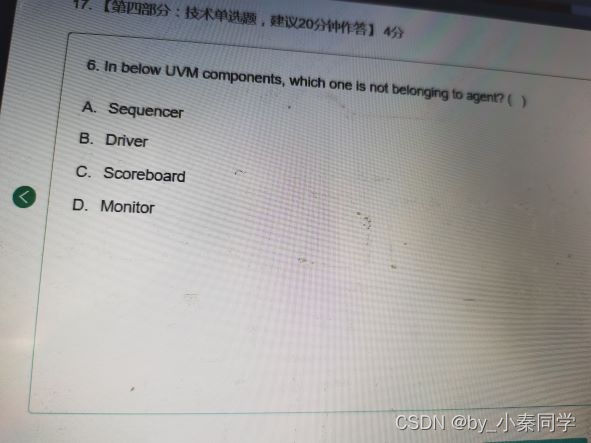

4.6 C

agent本身是一个包含sequencer、driver和monitor的容器.

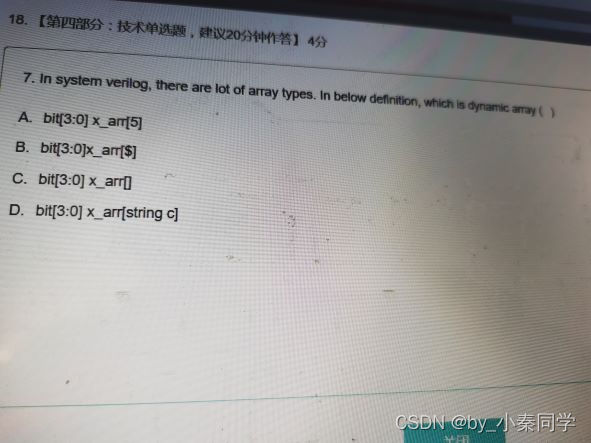

4.7 C

[]中没有数据,则为动态数组

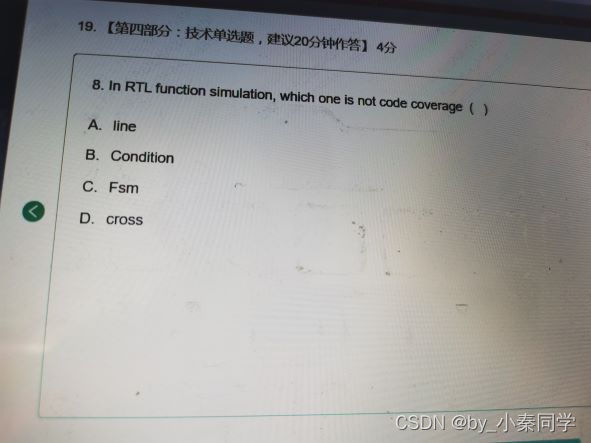

4.8 D

不会,也没查到,盲猜一波

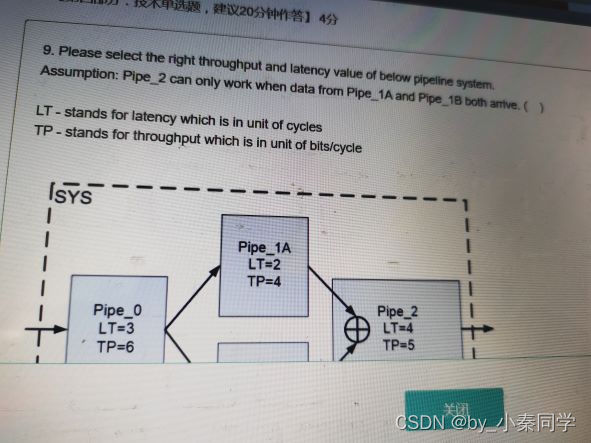

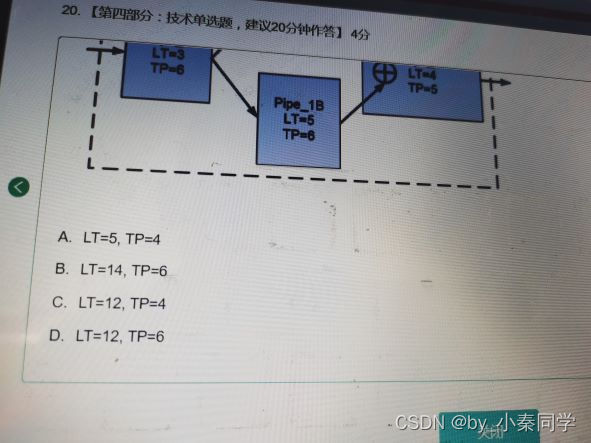

4.9 A

这个题我也没看懂,感觉是A。LT指的应该是流水线工作起来后的频率,而不是第一波处理的延时,pipe_1A和pipe_1B的处理需要按照慢的来算;TP这里我的考虑是pipe 0、1、2的最小吞吐量来选(个人看法)。

4.10 D

阻塞和非阻塞

4.11 B

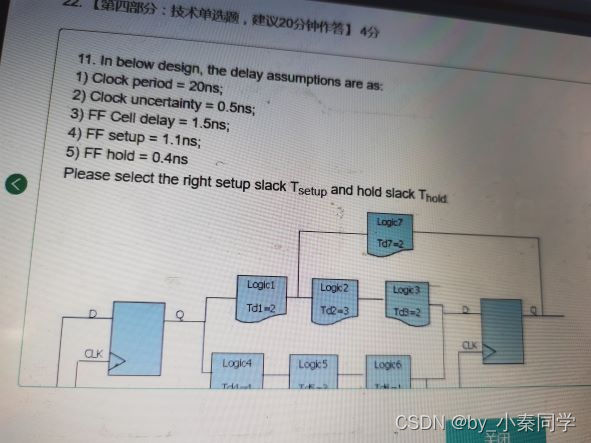

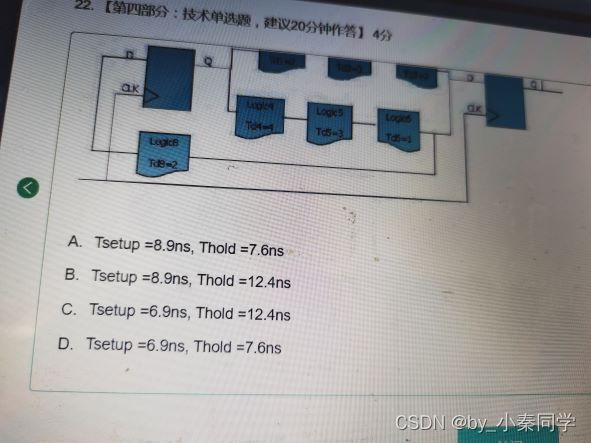

先求所需建立时间和保持时间,然后用周期减去这个计算的值,再减去给出的建立时间和保持时间后,就是建立和保持的裕量