前言

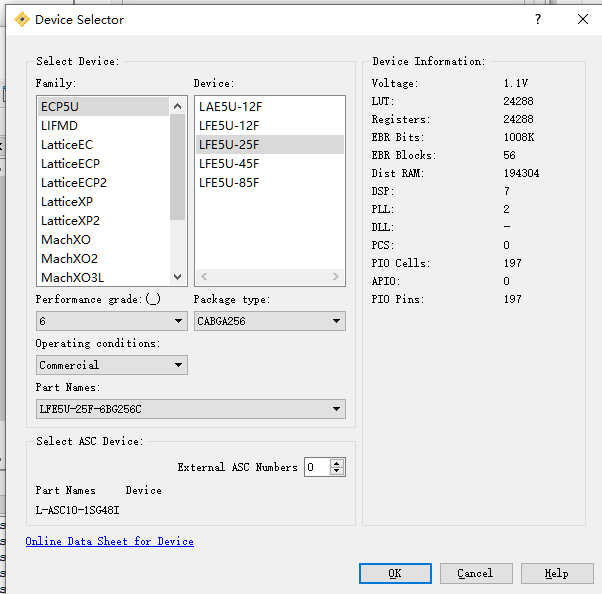

本实验FPGA基于LFE5U—25F一6BG256C,软件Lattice Diamond 3.10 (64-bit)和ModelSim SE-64 10.5

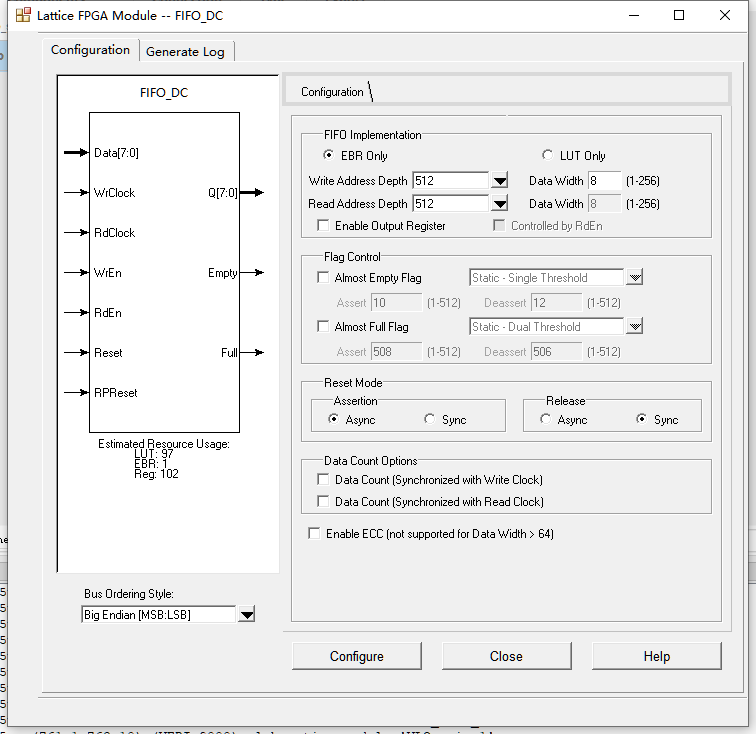

掌握基本使用方法后,调用FIFO的IP核,用Lattice联合ModelSim仿真。

一、添加IP

1.项目器件设置

具体参考02_LATTICE入门篇之新建项目

2.IP核配置

具体参考05_LATTICE入门篇之IP核

二、库文件添加

(一)方式一:添加器件库到ModelSim

此处参考Modelsim添加Lattice库

1.在modelsimF:\modeltech64_10.5目录下,新建一个文件夹,比如lattice,并进入此文件夹

2.新建一个名为sim.tcl的文本文件,输入如下脚本:

set DIAMOND_PATH F:/lscc/diamond/3.10_x64/cae_library/simulation/verilog

vlib work

vlib ec

vlib ecp

vlib ecp2

vlib ecp3

vlib ecp5u

vlib lptm

vlib lptm2

vlib machxo

vlib machxo2

vlib machxo3l

vlib pmi

vlib sc

vlib scm

vlib xp

vlib xp2

vlog -work ec $DIAMOND_PATH/ec/*.v

vlog -work ecp $DIAMOND_PATH/ecp/*.v

vlog -work ecp2 $DIAMOND_PATH/ecp2/*.v

vlog -work ecp3 $DIAMOND_PATH/ecp3/*.v

vlog -work ecp5u $DIAMOND_PATH/ecp5u/*.v

vlog -work lptm $DIAMOND_PATH/lptm/*.v

vlog -work lptm2 $DIAMOND_PATH/lptm2/*.v

vlog -work machxo $DIAMOND_PATH/machxo/*.v

vlog -work machxo2 $DIAMOND_PATH/machxo2/*.v

vlog -work machxo3l $DIAMOND_PATH/machxo3l/*.v

vlog -work pmi $DIAMOND_PATH/pmi/*.v

vlog -work sc $DIAMOND_PATH/sc/*.v

vlog -work scm $DIAMOND_PATH/scm/*.v

vlog -work xp $DIAMOND_PATH/xp/*.v

vlog -work xp2 $DIAMOND_PATH/xp2/*.v

3.运行脚本

打开命令提示符进入sim.tcl 所在F:\modeltech64_10.5\lattice目录下

运行脚本

vsim -do sim.tcl

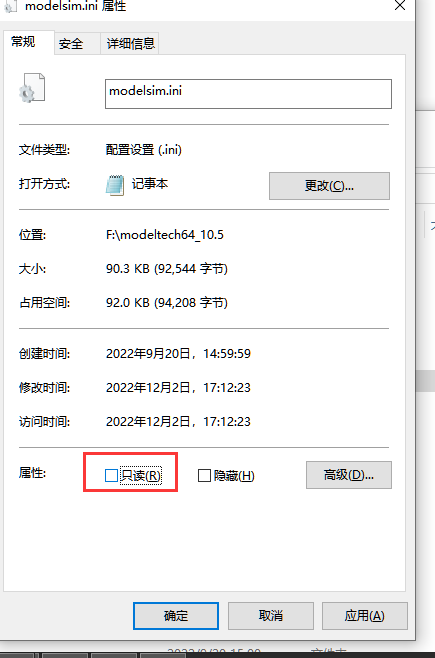

4.回到modesim主目录:F:\modeltech64_10.5,找到modelsim.ini文件,右键->将“只读”属性去掉。

5.然后再打开modelsim.ini,在[Library]这个标签后,添加如下:

ec = $MODEL_TECH/../lattice/ec

ecp = $MODEL_TECH/../lattice/ecp

ecp2 = $MODEL_TECH/../lattice/ecp2

ecp3 = $MODEL_TECH/../lattice/ecp3

ecp5u = $MODEL_TECH/../lattice/ecp5u

lptm = $MODEL_TECH/../lattice/lptm

lptm2 = $MODEL_TECH/../lattice/lptm2

machxo = $MODEL_TECH/../lattice/machxo

machxo2 = $MODEL_TECH/../lattice/machxo2

machxo3l = $MODEL_TECH/../lattice/machxo3l

pmi = $MODEL_TECH/../lattice/pmi

sc = $MODEL_TECH/../lattice/sc

scm = $MODEL_TECH/../lattice/scm

xp = $MODEL_TECH/../lattice/xp

xp2 = $MODEL_TECH/../lattice/xp2

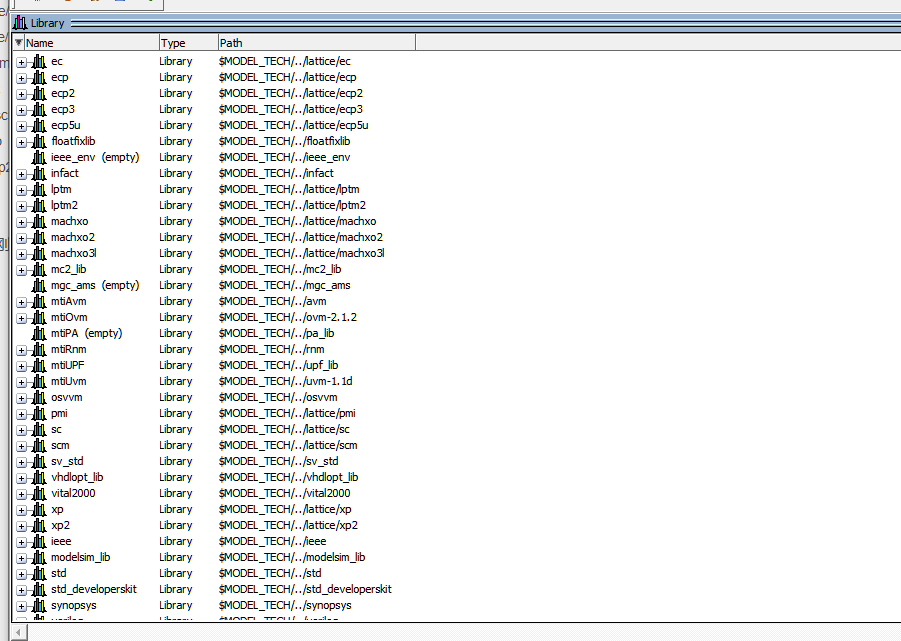

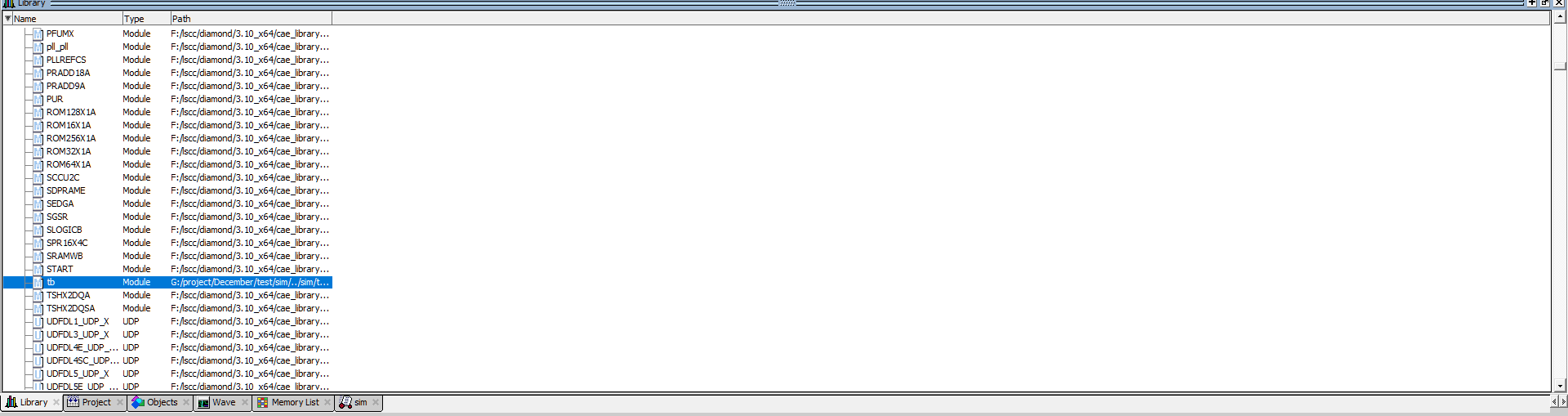

6.保存modelsim.ini,然后关闭刚modelsim重启,看到库的情况如下:

7.回到modesim主目录:F:\modeltech64_10.5,找到modelsim.ini文件,右键->增加“只读”属性。

附:这个方法添加了器件库后,编译没有问题,但是新建库仿真跑波形又会报错提示找不到对应的库对应.v了,很奇怪。猜测可能是添加的库文件.v和需要仿真的.v不在同一个Libray中,也可能是其他.所以用了下面的方法,解决。

(二)方法二:直接添加器件库到Libray,和tb.v在同一个目录下仿真

此处参考Lattice Diamond与modelsim联合仿真环境设置

1… 选中空库(work))

2.点击modelsim的菜单栏中选择Compile >> Compile,

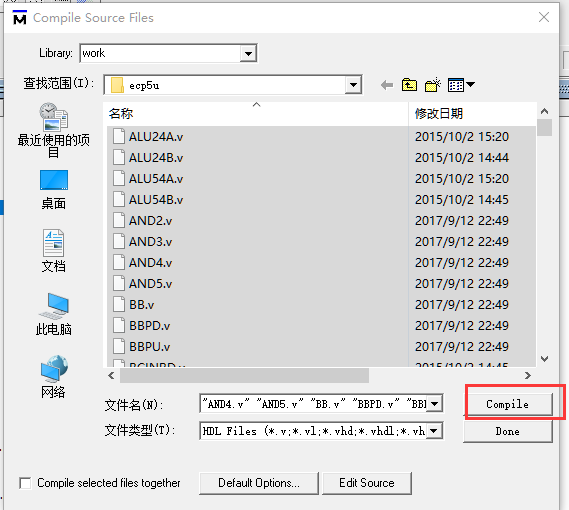

3.找到F:\lscc\diamond\3.10_x64\cae_library\simulation\verilog目录下对应器件库ecp5u下的所有.v,Ctrl+A全选点击Complie,编译完成点击Done,

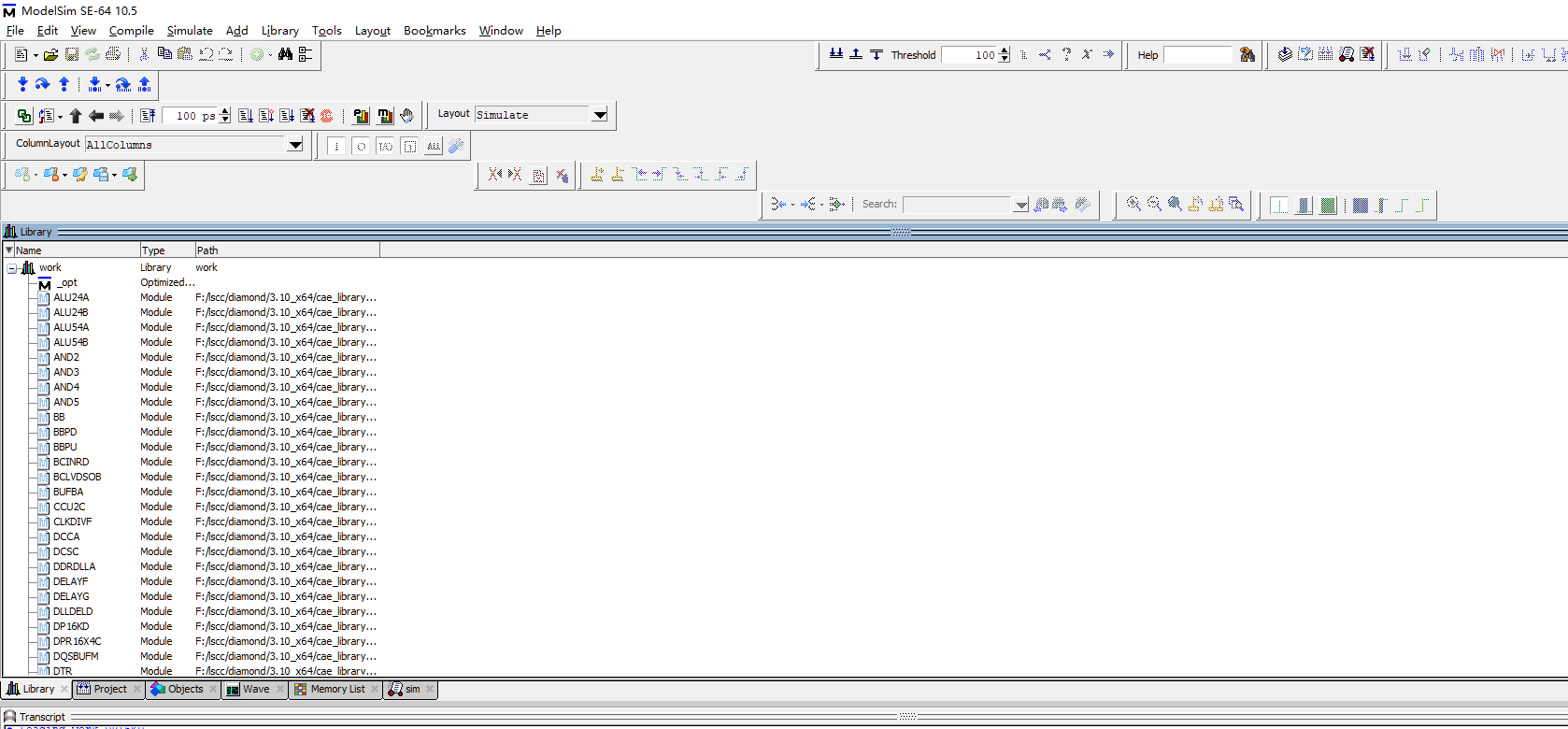

5.完成后可以看见库文件和tb文件全在同一个Library下了,再仿真,没有报错了。

除了找仿真文件tb.v的时候有点麻烦,其他的没什么问题。

三、仿真

下面是利用脚本进行仿真

(一)仿真文件

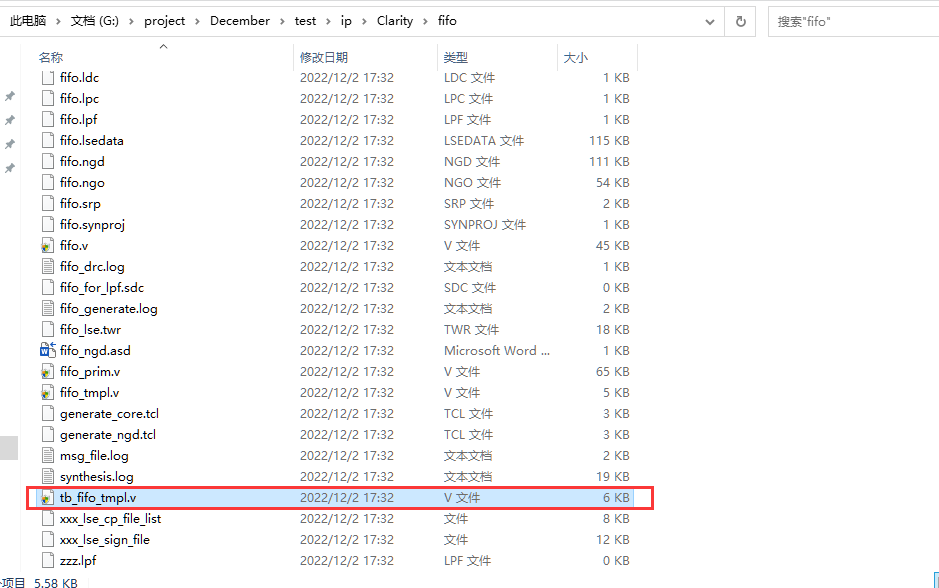

1.再添加ip时,Diamond会自动添加仿真文件,只需略微修改即可或者不修改也行。

2.tb文件,放到项目仿真目录下

`timescale 1 ns / 1 ps

module tb;

GSR GSR_INST (.GSR(1'b1));

PUR PUR_INST (.PUR(1'b1));

reg [7:0] Data = 8'b0;

reg WrClock = 0;

reg RdClock = 0;

reg WrEn = 0;

reg RdEn = 0;

reg Reset = 0;

reg RPReset = 0;

wire [7:0] Q;

wire Empty;

wire Full;

integer i0 = 0, i1 = 0, i2 = 0, i3 = 0, i4 = 0, i5 = 0, i6 = 0, i7 = 0, i8 = 0, i9 = 0;

fifo u1 (.Data(Data), .WrClock(WrClock), .RdClock(RdClock), .WrEn(WrEn),

.RdEn(RdEn), .Reset(Reset), .RPReset(RPReset), .Q(Q), .Empty(Empty),

.Full(Full)

);

initial

begin

Data <= 0;

#100;

@(Reset == 1'b0);

for (i1 = 0; i1 < 515; i1 = i1 + 1) begin

@(posedge WrClock);

Data <= Data + 1'b1;

@(posedge WrClock);

end

end

always

#5.00 WrClock <= ~ WrClock;

always

#5.00 RdClock <= ~ RdClock;

initial

begin

WrEn <= 1'b0;

#100;

@(Reset == 1'b0);

for (i4 = 0; i4 < 515; i4 = i4 + 1) begin

@(posedge WrClock);

#1 WrEn <= 1'b1;

@(posedge WrClock);

#1 WrEn <= 1'b0;

end

WrEn <= 1'b0;

#200;

$stop;

end

initial

begin

RdEn <= 1'b0;

@(Reset == 1'b0);

@(WrEn == 1'b1);

@(WrEn == 1'b0);

for (i5 = 0; i5 < 515; i5 = i5 + 1) begin

@(posedge RdClock);

#1 RdEn <= 1'b1;

@(posedge RdClock);

#1 RdEn <= 1'b0;

end

RdEn <= 1'b0;

#200;

$stop;

end

initial

begin

Reset <= 1'b1;

#100;

Reset <= 1'b0;

end

initial

begin

RPReset <= 1'b1;

#100;

RPReset <= 1'b0;

end

endmodule

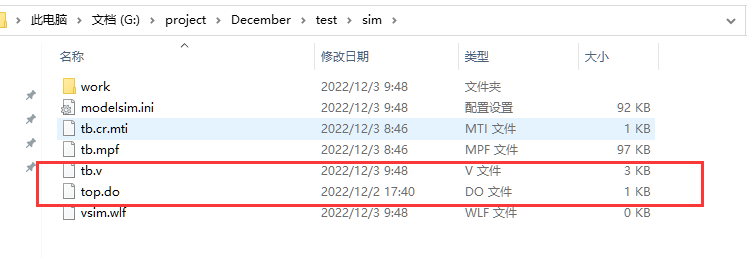

3.脚本文件top.do

vlib work

vmap work work

#编译testbench文件

vlog ../sim/tb.v

#编译 设计文件

vlog ../ip/Clarity/fifo/fifo.v

#添加库文件

#指定仿真顶层

vsim -novopt work.tb

#添加信号到波形窗

add wave -position insertpoint sim:/tb//*

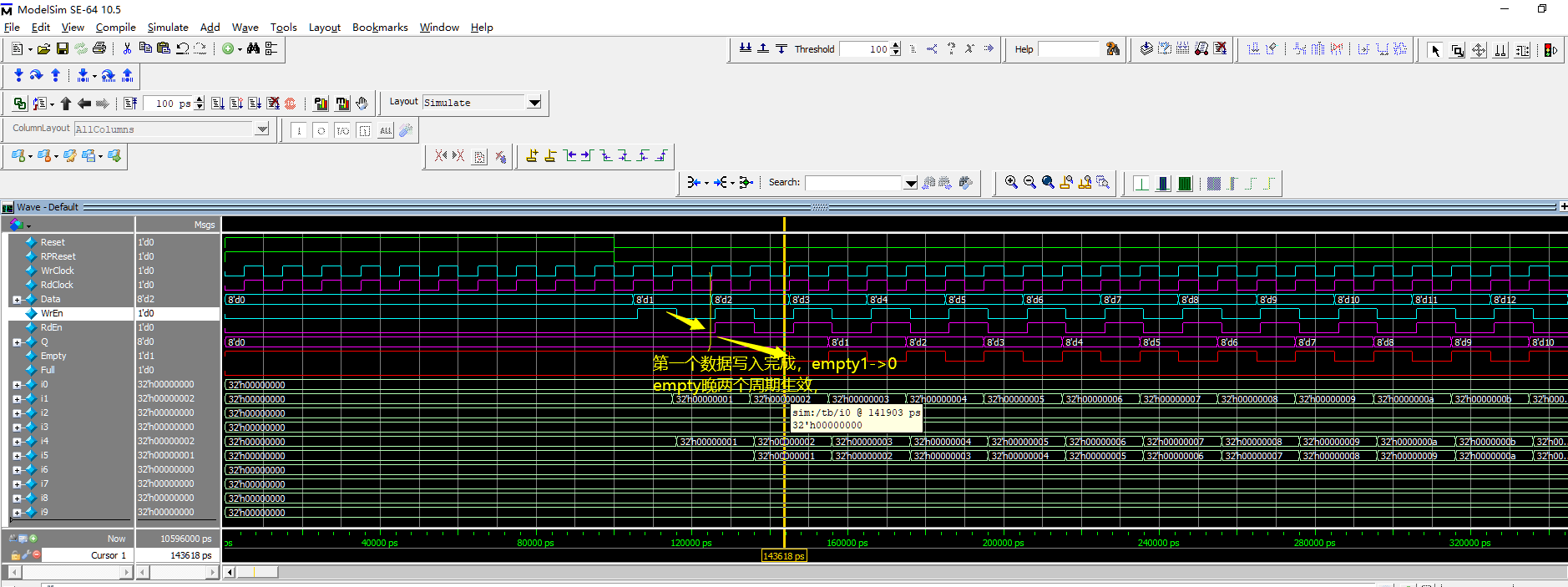

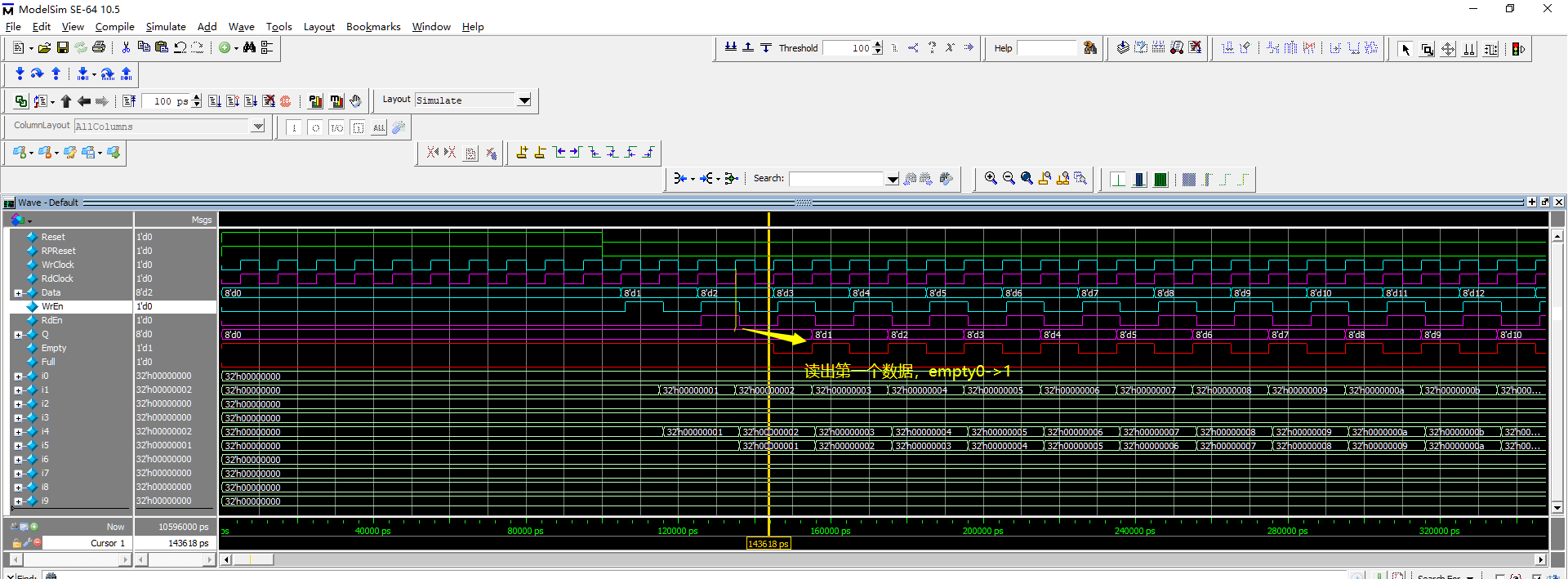

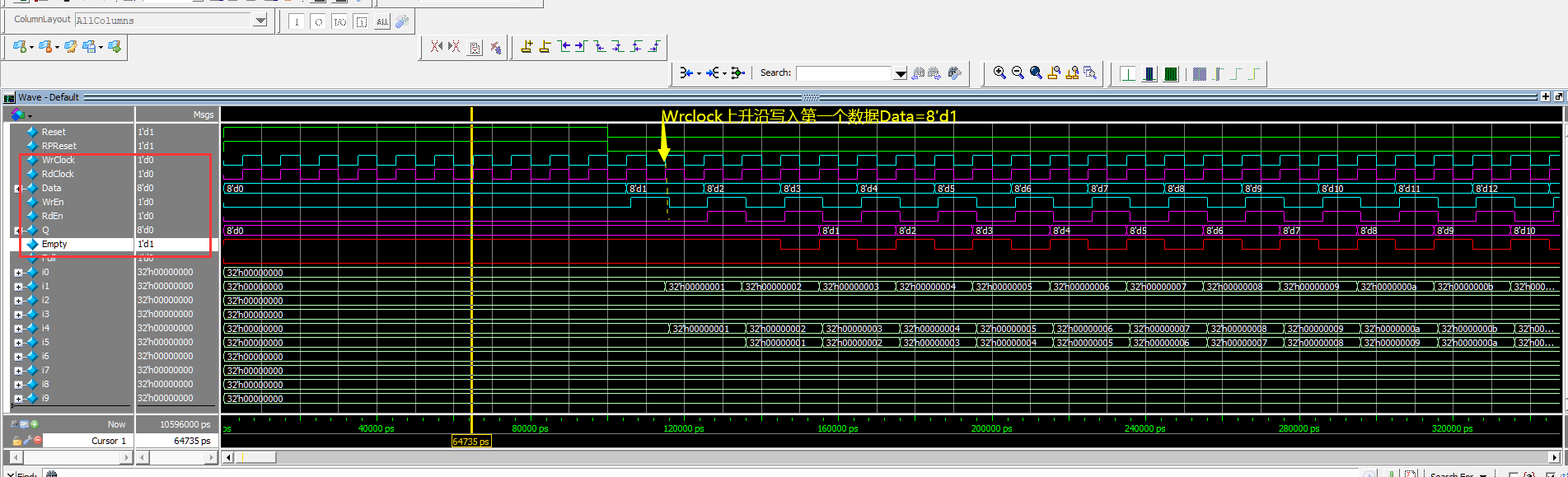

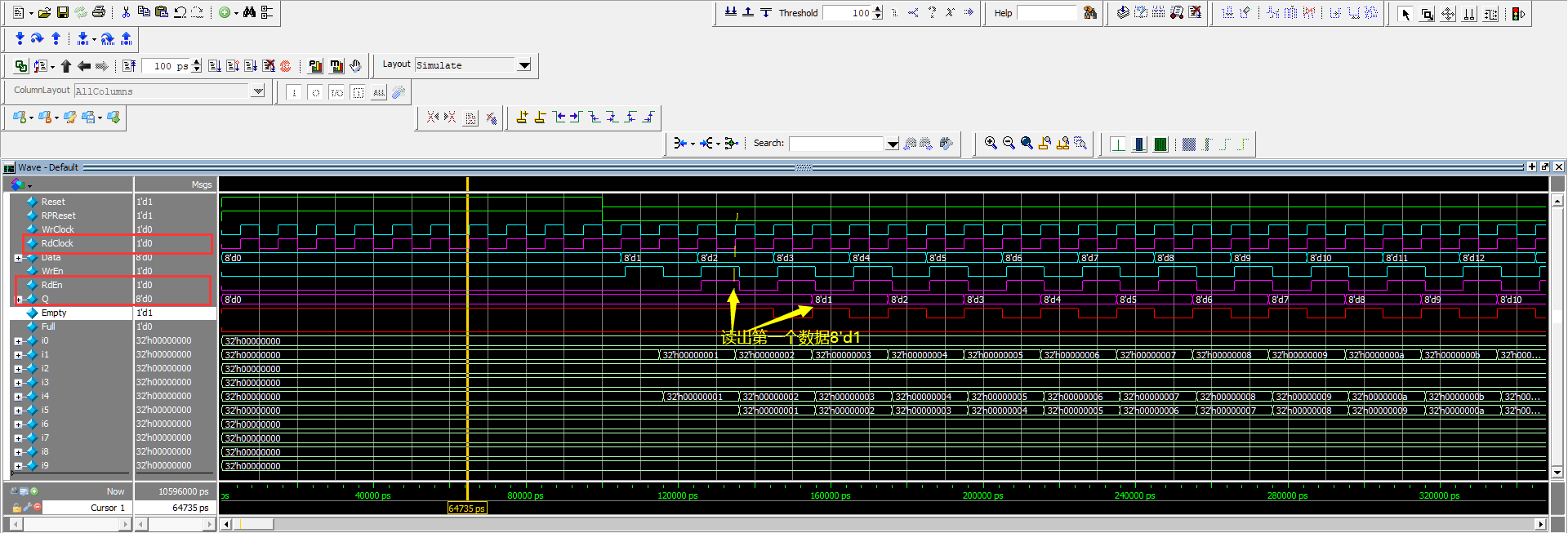

(二)仿真结果

对照参考Lattice系列内存时序

之六、双端口FIFO(FIFO_DC) – 基于 EBR 或 LUT

1.写入第一个数据

WrEn=1:Wrclock上升沿写入第一个数据Data=8’d1

2.读出数据

RrEn=1:Rrclock上升沿写入第一个数据Q=8’d1

3,关于empty

empty延迟了两个周期生效