PAD2Reg:

1)Input delay约束从SOC PAD输入到第一级FF的data path;

2)Input delay约束中的-clock指的是launch clock,它一般存在于Device中,对SOC来说是个虚拟时钟,如果发射采样是同沿的,你可能感觉不出来,如果不同沿,约束写错的影响就大了;

3)max对应setup分析,value越大时序越紧;

4)min对应hold分析,value越小时序越紧;

5)delay value = source clock delay + data path delay - destination clock delay;

6)以SOC PAD为边界,所有SOC内部的delay信息都是不可知的,不要算到delay value里面去,那是工具的活;

7)如果没有外部器件的时序信息,我们可以人为设置严格一点的值,max(setup)可以取60%~70%时钟周期,而min(hold)可以取0甚至-1,从而保证即使clk和data完全对齐,甚至data比clk还早一点到,也不会引发hold违例;

8)即使input完全是async的,我们也希望对它的路径可控,可以用其采样时钟进行约束(如果它连采样时钟都没有,那就可以设置false path了);

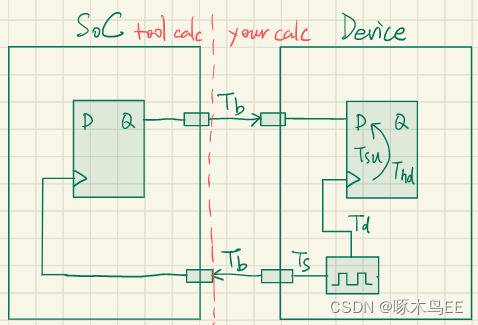

9)Tb指的是PCB板级延时,通常data routing和clock routing会做等长,所以这里统一标记为Tb。如果Device和SOC在一个板子上,一般走线不会很长,Tb大概率不会超过1ns(PCB走线延时0.14~0.17ns/inch),但如果是通过cable连接的母板和子板,板级延时就不得不慎重考虑了。

case-1: source synchronous with forward clock

Input delay = Ts + Tco + Tb - Td - Tb = Tco (max/min)

case-2: source synchronous with backward clock

Input delay = Tb + Ts + Tco + Tb = 2*Tb + Tco (max/min) (注:忽略Ts)

Reg2PAD:

1)Output delay约束从SOC PAD输出到Device第一级FF的data path;

2)Output delay约束中的-clock指的是capture clock,它一般存在于Device中,对SOC来说是个虚拟时钟,如果发射采样是同沿的,你可能感觉不出来,如果不同沿,约束写错的影响就大了;

3)max对应setup分析,value越大时序越紧;

4)min对应hold分析,value越小时序越紧;

5)max delay value = source clock delay + data path delay + device setup time - destination clock delay;

6)min delay value = source clock delay + data path delay - device hold time - destination clock delay;

7)以SOC PAD为边界,所有SOC内部的delay信息都是不可知的,不要算到delay value里面去,那是工具的活;

8)如果没有外部器件的时序信息,我们可以人为设置严格一点的值,max(setup)可以取60%~70%时钟周期,而min(hold)可以取0甚至-1,从而保证即使clk和data完全对齐,甚至data比clk还早一点到,也不会引发hold违例;

9)即使output完全是async的,我们也希望对它的路径可控,可以用其发射时钟进行约束(如果它连发射时钟都没有,那就可以设置false path了);

10)Tb指的是PCB板级延时,通常data routing和clock routing会做等长,所以这里统一标记为Tb。如果Device和SOC在一个板子上,一般走线不会很长,Tb大概率不会超过1ns(PCB走线延时0.14~0.17ns/inch),但如果是通过cable连接的母板和子板,板级延时就不得不慎重考虑了。

case-1: source synchronous with forward clock

max output delay = Tb + Tsu - Tb - Td = Tsu (注:忽略Td)

min output delay = Tb - Thd - Tb - Td = -Thd (注:忽略Td)

case-2: source synchronous with backward clock

max output delay = Ts + 2*Tb + Tsu - Td = 2*Tb + Tsu (注:认为Ts = Td)

min output delay = Ts + 2*Tb - Thd - Td = 2*Tb - Thd (注:认为Ts = Td)