在进行时序分析时,经常会遇到两个比较容易混淆的概念,那就是时钟抖动(Clock Jitter)和时钟偏斜(Clock Skew)。下面就解释下两者的区别:

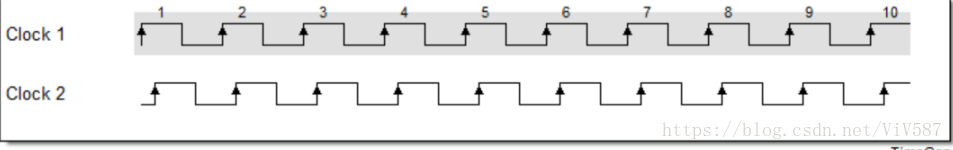

一、Jitter

由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。也即相对于理想时钟沿产生的不随时间积累的、时而超前、时而滞后的偏移。它指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。由于跟晶振本身的工艺有关,所以在设计中无法避免它能带来的影响,通产只能在设计中留有一定的margin。

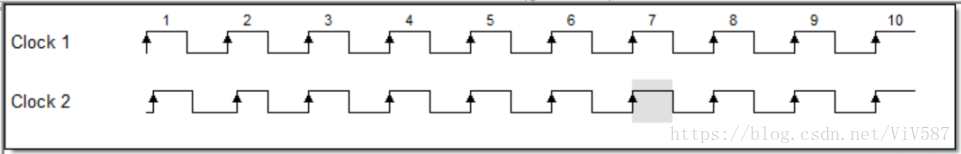

二、Skew

是指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。完成布局布线后,物理路径延时是固定的,所以在设计中考虑到时钟偏斜,就可以避免偏斜带来的影响。