提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

所谓“频率”,就是周期性信号在单位时间(秒)内变化的次数。

一、频率计是什么

所谓“频率”,就是周期性信号在单位时间(秒)内变化的次数。若在一定的时间间隔T内计数,计得某周期性信号的重复变化次数为N,则该信号的频率可表达为:

f =N/ T

所以测量频率就要分别知道N和T的值,由此,测量频率的方法一般有三种:测频方法、测周方法和等精度测量。

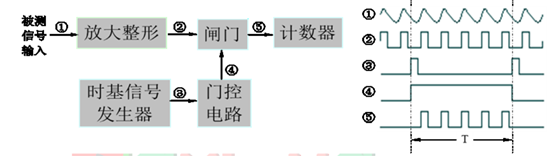

测频方法:这种方法即己知时基信号(频率或周期确定)做门控信号,T为已知量,然后在门控信号有效的时间段内进行输入脉冲的计数,原理图如下图所示:

二、使用步骤

1.测量方法

首先,被测信号①(以正弦波为例)经过放大整形后转变成方波脉冲②,其重复频率等于被测信号频率。把方波脉冲②加到闸门的输入端。由一个高稳定的石英振荡器和一系列数字分频器组成了时基信号发生器,它输出时间基准(或频率基准)信号③去控制门控电路形成门控信号④,门控信号的作用时间T是非常准确的(由石英振荡器决定)。门控信号控制闸门的开与闭,只有在闸门开通的时间内,方波脉冲②才能通过闸门成为被计数的脉冲⑤由计数器计数。闸门开通的时间称为闸门时间,其长度等于门控信号作用时间T。比如,时间基准信号的重复周期为1S,加到闸门的门控信号作用时间T亦准确地等于1S,即闸门的开通时间——“闸门时间”为1S。在这一段时间内,若计数器计得N=100000个数,根据公式f =N /T,那么被测频率就是100000Hz。如果计数式频率计的显示器单位为“KHz”,则显示100.000KHz,即小数点定位在第三位。不难设想,若将闸门时间设为T=0.1S,则计数值为10000,这时,显示器的小数点只要根据闸门时间

T的改变也随之自动往右移动一位(自动定位),那么,显示的结果为100.00Khz。在计数式数字频率计中,通过选择不同的闸门时间,可以改变频率计的测量范围和测量精度。

2.测周方法:

测周方法:

被测信号(频率或周期待测)做门控信号,T为未知量,做门控信号T,然后在门控信号有效的时间段内对时基信号脉冲计数,原理图如下图所示: 测周方法:

等精度测量法的核心思想是通过闸门信号与被测信号同步,将闸门时间t控制为被测信号周期长度的整数倍。测量时,先打开预置闸门,当检测到被测信号脉冲沿到达时,标准信号时钟开始计数。预置闸门关闭时,标准信号并不立即停止计数,而是等检测到被测信号脉冲沿到达时才停止,完成被测信号整数个周期的测量。测量的实际闸门时间可能会与预置闸门时间不完全相同,但最大差值不会超过被测信号的一个周期。在等精度测量法中,相对误差与被测信号本身的频率特性无关,即对整个测量域而言,测量精度相等,因而称之为“等精度测量”。标准信号的计数值越大则测量相对误差越小,即提高门限时间r和标准信号频率f。可以提高测量精度。在精度不变的情况下,提高标准信号频率可以缩短门限时间,提高测量速度。

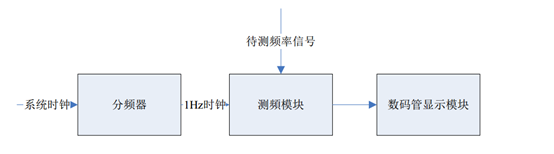

3.系统框图

/***********************产生测试时钟**************************************/

always @(posedge sysclk)

begin

if(counter==15'b110_0001_1010_1000)

begin

test_clk<=~test_clk;//500HZ

counter<=15'b0;

end

else

counter<=counter+1'b1;

end

/**********************产生1HZ的时钟************************************/

always @(posedge sysclk)

begin

if(clk_counter==25'b1_0111_1101_0111_1000_0100_0000)

begin

clk_div<=~clk_div;

clk_counter<=25'b0;

end

else

clk_counter<=clk_counter+1'b1;

end

/*********************测试待测信号***********************************/

always @(posedge inclk)

begin

if(clk_div)

begin

if(counter1==4'b1001)

begin

counter1<=4'b0;

counter2<=counter2+1'b1;

if(counter2==4'b1001)

begin

counter2<=4'b0;

counter3<=counter3+1'b1;

if(counter3==4'b1001)

begin

counter3<=4'b0;

counter4<=counter4+1'b1;

if(counter4==4'b1001)

begin

counter4<=4'b0;

counter5<=counter5+1'b1;

if(counter5==4'b1001)

begin

counter5<=4'b0;

counter6<=counter6+1'b1;

if(counter6==4'b1001)

begin

counter6<=4'b0;

counter7<=counter7+1'b1;

if(counter7==4'b1001)

begin

counter7<=4'b0;

counter8<=counter8+1'b1;

if(counter8==4'b1001)

begin

counter8<=4'b0;

end

end

end

end

end

end

end

end

else

counter1<=counter1+1'b1;

end

else

总结

可以使用PLL生成时钟进行测试