写在前面:无论是在 ISE 还是 Vivado 中,关于 IP核 的调用都是非常方便的,所以对于初学者来说最关键的不是在 IP Catalog 中设置相关的 IP核 参数,而是在生成相关的 IP核 后该怎么做,也即如何让这些 IP核 为项目工程服务。

接下来,以 MMCM / PLL IP 核作为实例,在 Vivado 中演示该 IP 核的实现及进一步操作,包括测试仿真文件TestBench的实现思想。

本文的关键在于下文实验步骤的第二项 -->"怎么使用这个生成的用户IP"

实验任务

时钟输入为50MHz,输出三个时钟:

(1).第一个输出时钟为100MHz,无相位偏移;

(2).第二个输出时钟为25MHz ,无相位偏移;

(3).第三个输出时钟为100MHz,180度相偏。

实验步骤

一、IP Catalog创建用户 IP

1.首先创建一个空的工程,工程名为“ip_clk”。接下来添加 IP 核。在 Vivado 软件的左侧“Flow Navigator”栏中单击“IP Catalog”。

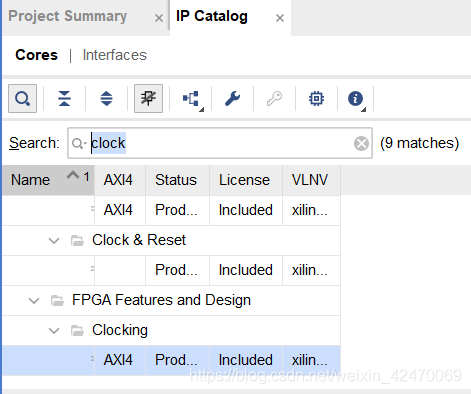

2.打开“IP Catalog”窗口后,在搜索栏中输入“clock”关键字,如下图所示。

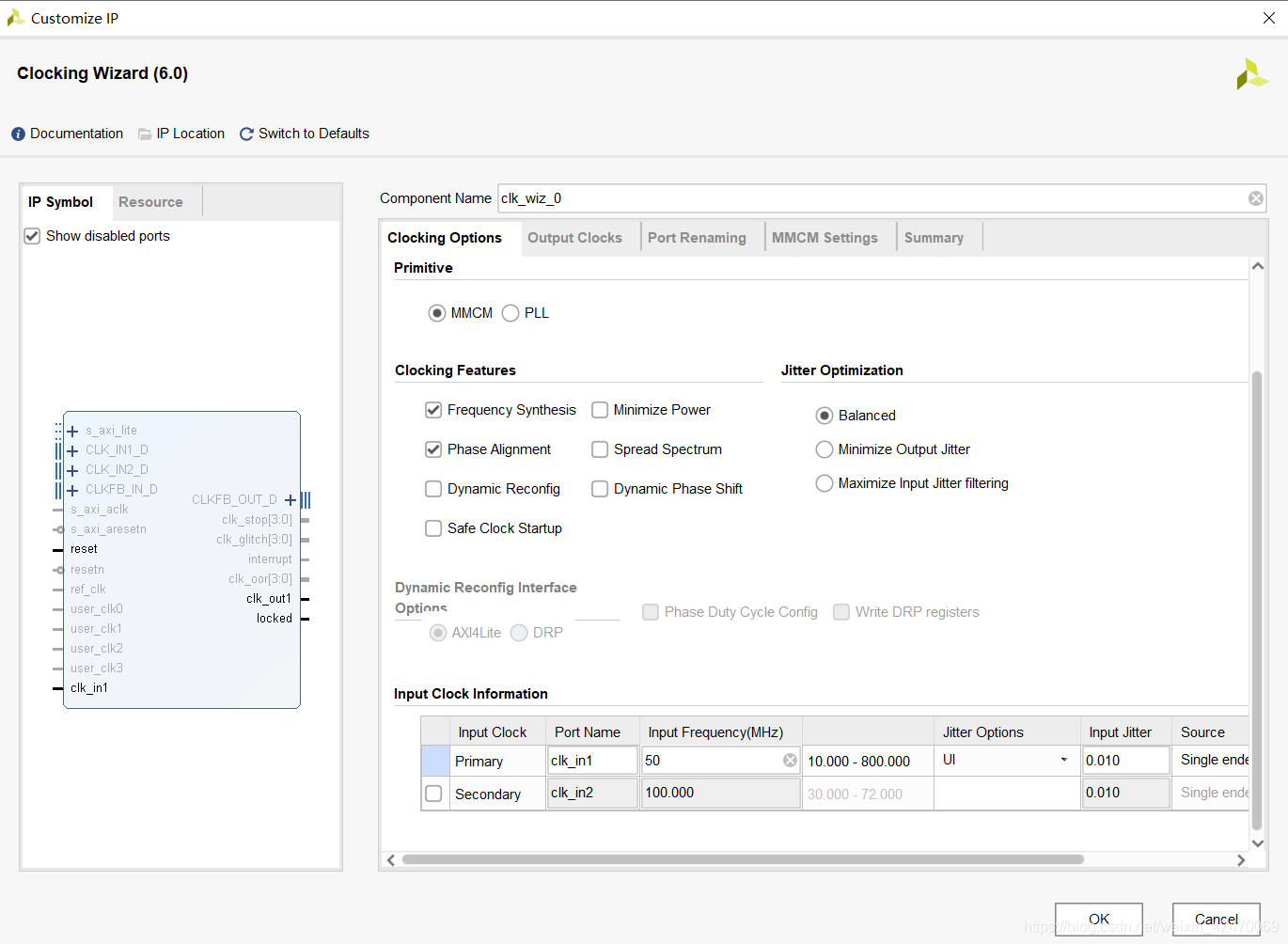

3.双击“FPGA Features and Design”的“Clocking”下的“Clocking Wizard”,弹出“Customize IP”窗口,如下图所示。

4.配置 IP 核的时钟参数。

最上面的“Component Name”一栏设置用户 IP 的名称,保持默认即可。最下面的“Input Clock Information”一栏,把“Primary”时钟的输入频率修改为实验任务中要求的50MHz输入频率。

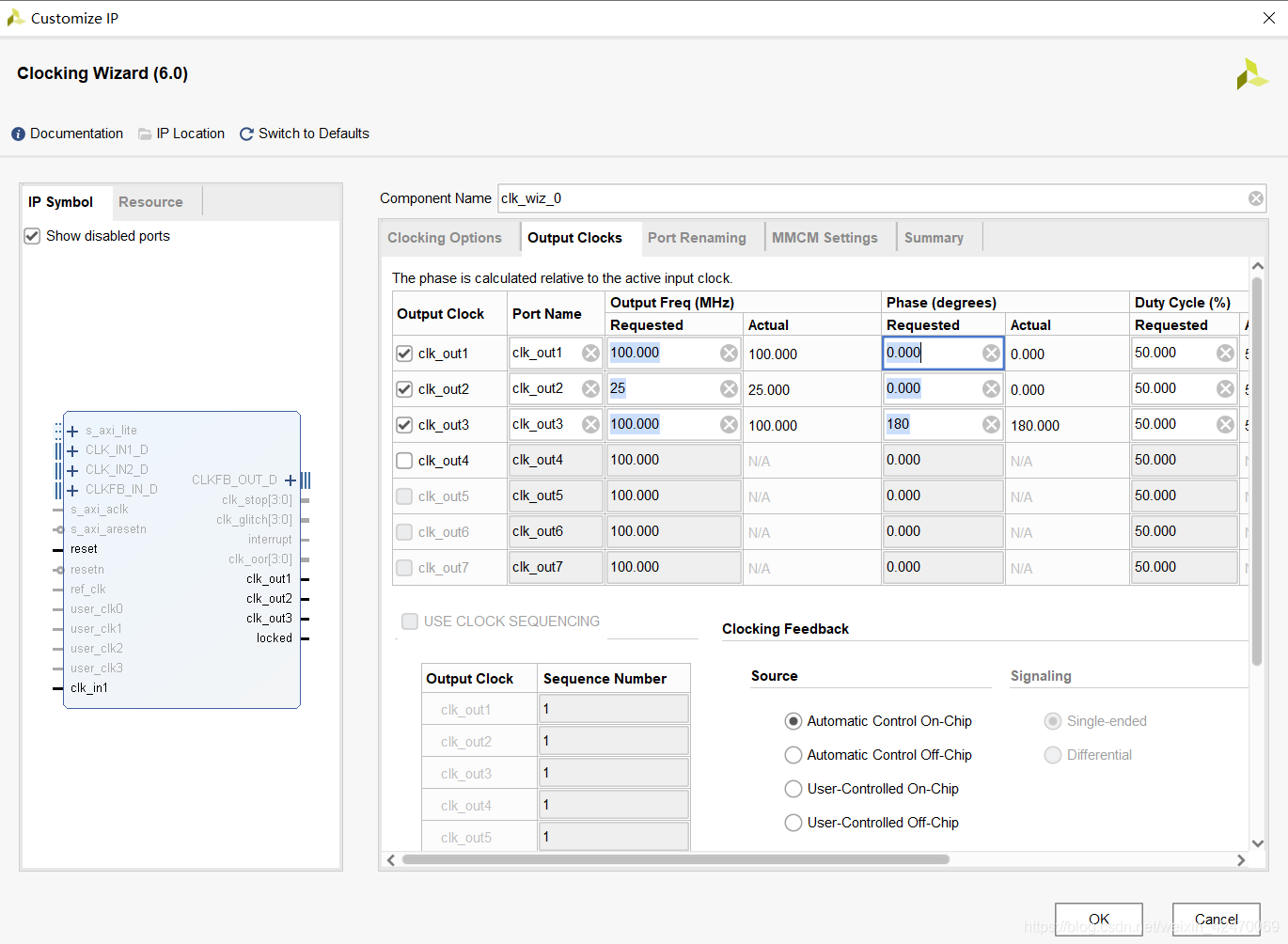

5.切换至“Output Clocks”选项卡,在“Output Clock”选项卡中,勾选前 3 个时钟,并且将其“Output Freq(MHz)”分别设置为 100、50、100,“Phase(degrees)”一栏分别设置为0、0、180。其他设置保持默认即可,如下图所示。

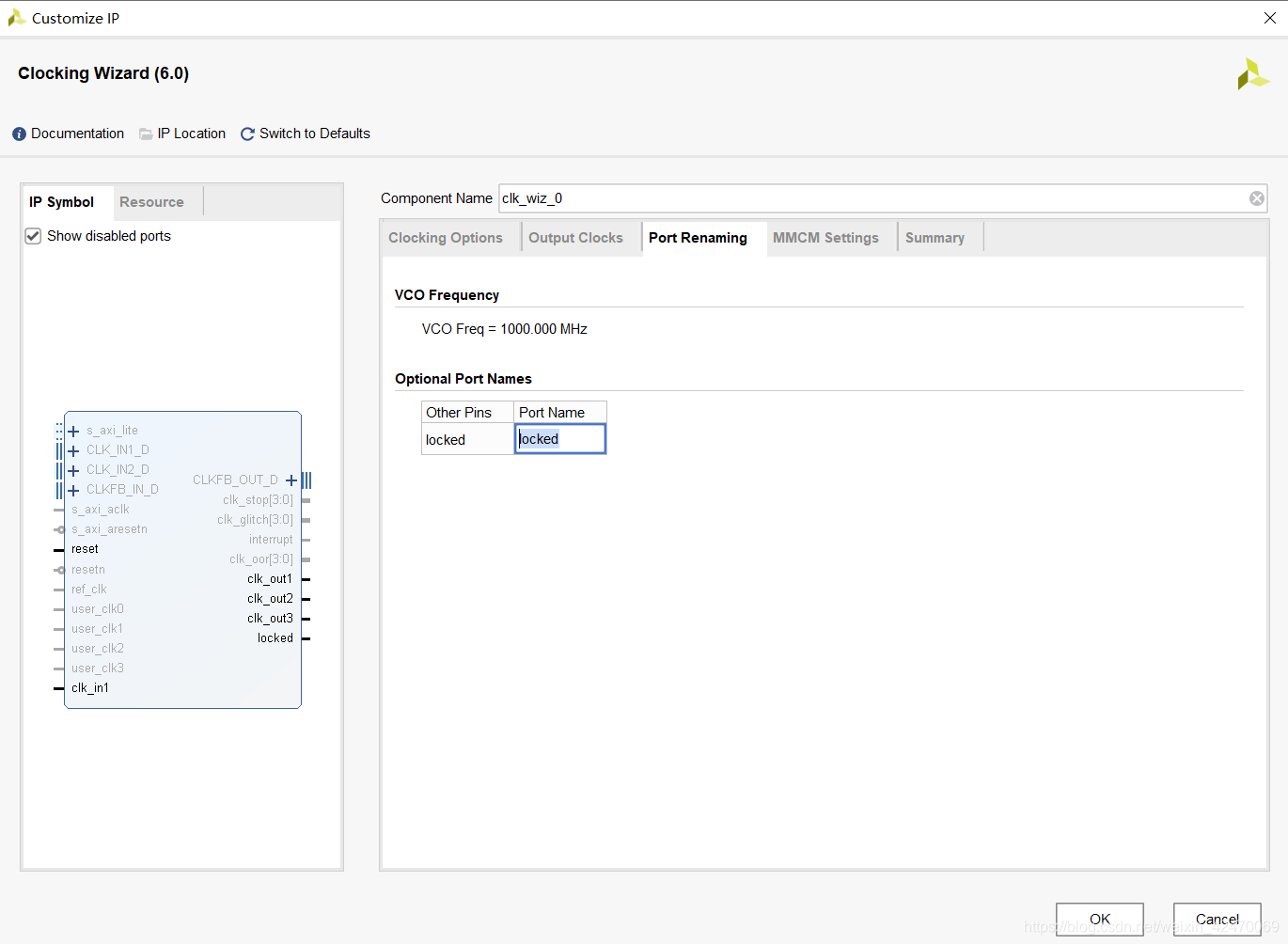

6.“Port Renaming”选项卡和“MMCM Setting”选项卡不变。

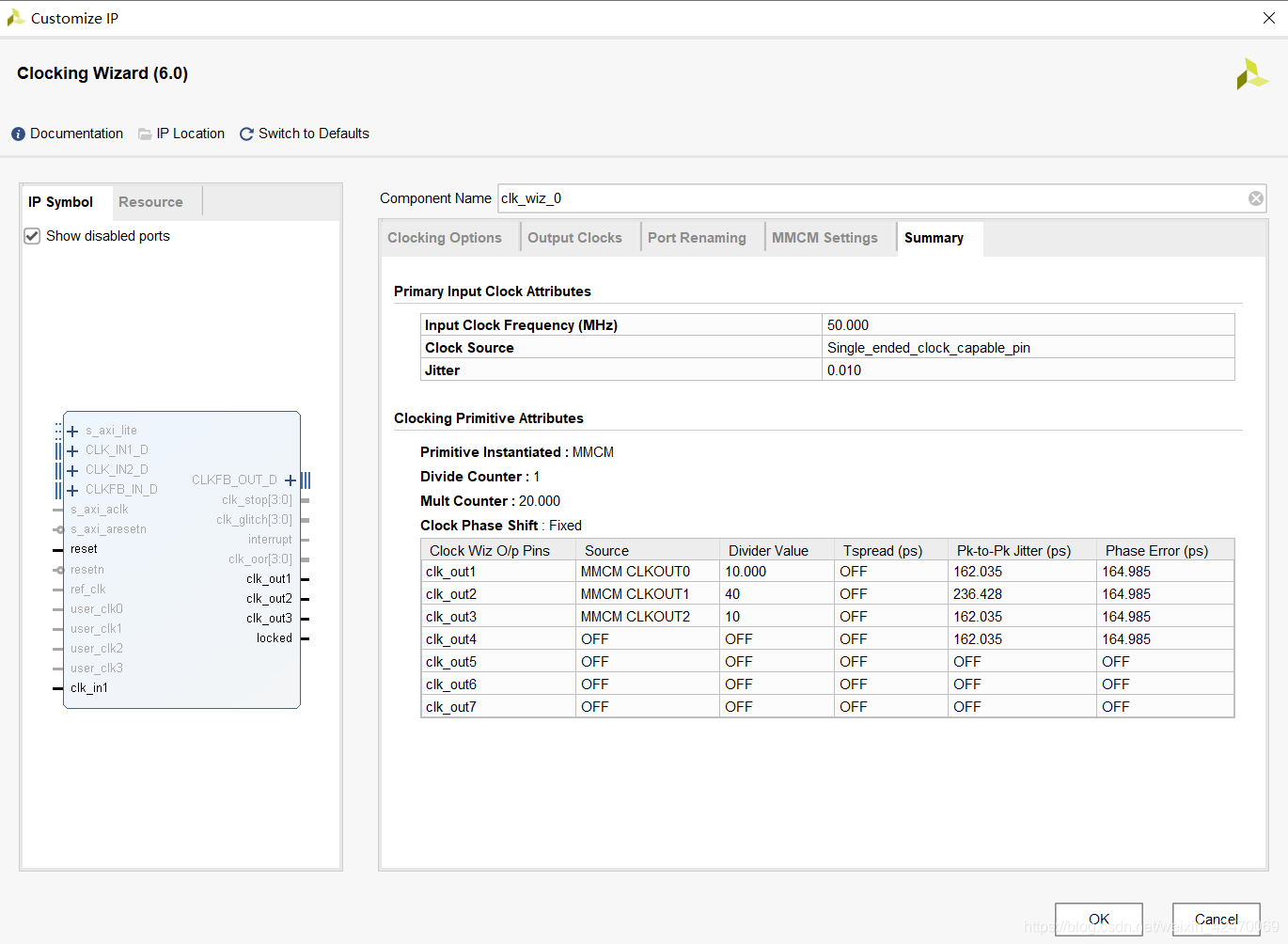

7.最后的“Summary”选项卡是对前面所有配置的一个总结,直接点击“OK”,如下图所示。

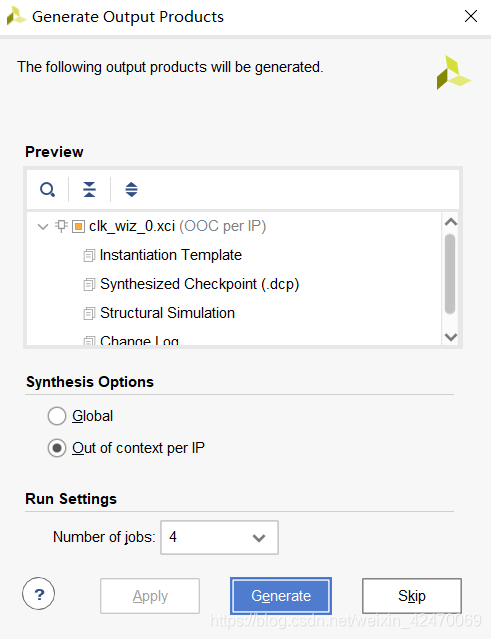

8.接着就弹出了“Genarate Output Products”窗口,直接点击“Generate”,如下图所示。

二、怎么使用这个生成的用户IP

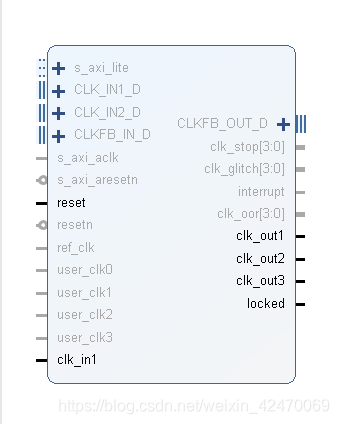

在创建完上面的IP核后,还不能直接达到实验任务的要求,先看看生成的用户IP模块图。

左侧最下面的输入管脚“clk_in1”是需要外接晶振来提供50MHz的时钟的,以及左侧中间的输入管脚“reset”也需要外接管脚来实现。

所以接下来需要创建一个 verilog 源文件,其名称为“ ip_clk.v”,为其提供以上要求的两个输入,实质也就是为生成的用户IP文件“clk_wiz_0.xci”例化,代码如下:

module ip_clk(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//输出时钟

output clk_100m , //100Mhz 时钟频率

output clk_25m, //25Mhz 时钟频率

output clk_100m_180deg //100Mhz 时钟频率,相位偏移 180 度

);

wire locked;

//MMCM IP 核的例化

clk_wiz_0 clk_wiz_0(

.clk_out1 (clk_100m),

.clk_out2 (clk_25m),

.clk_out3 (clk_100m_180deg),

.reset (~sys_rst_n), // input reset,该IP高低平复位,故取反

.locked (locked), // output locked

.clk_in1 (sys_clk) // input clk_in1

);

endmodul

那么仿真测试TestBench文件,也就是相当于给“ ip_clk.v”提供晶振时钟输入以及复位引脚。

module tb_ip_clk();

reg sys_clk;

reg sys_rst_n;

wire clk_100m;

wire clk_25m;

wire clk_100m_180deg;

always #10 sys_clk = ~sys_clk;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

ip_clk u_ip_clk(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.clk_100m (clk_100m ),

.clk_25m (clk_25m ) ,

.clk_100m_180deg (clk_100m_180deg)

);

endmodule

IP核的出现极大的便利工程的实现,提供了稳定的“黑盒子”,但这个黑盒子不给它输入,就仅仅是个盒子。

对于更复杂的IP核调用以及后续使用道理一样。