时序分析约束

时序分析:时序分析的目的就是通过分析fpga设计各个寄存器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟之间的关系。保证整个系统中的所有寄存器都能正确存储数据。

时序约束:两个作用

1、 告知EDA软件,该设计需要达到怎么样的时序指标,然后EDA软件会根据时序约束的各个参数,尽力优化布局布线,以达到该约束指标

2、 协助EDA软件进行分析设计的时序路径,以产生相应的时序报告。

分析系统:

分析建立时间余量的时候,看85度慢速模型下的报告

分析保持时间余量的时候,看0度快速模型下的报告

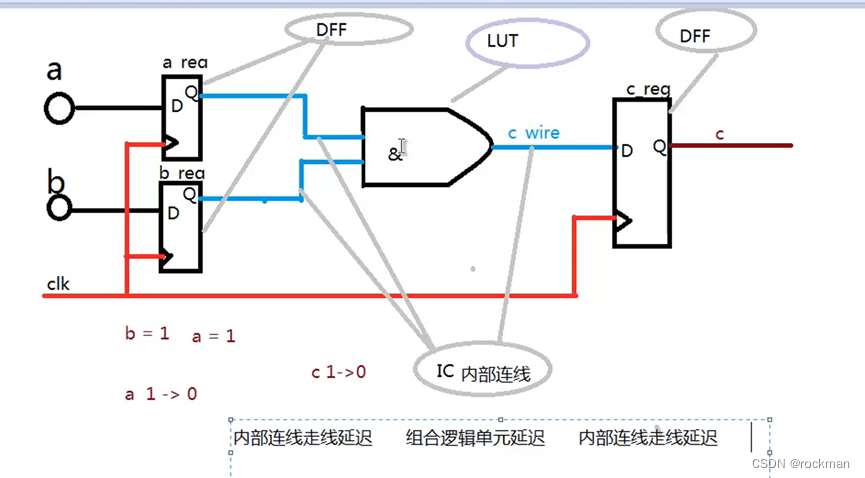

一、 了解fpga内部传输模型

Input clk;

Input a;

Input b;

Output reg c;

Reg a_reg;

Reg b_reg;

Wire c_wire;

Always(posedge clk)begin

a_reg <= a;

b_reg <= b;

end

assign c_wire = a_reg & b_reg;

always(posedge clk)

c <= c_wire;

模型:

时序约束的要求:要求数据从寄存器a Q端发出经过IC内部连线、lut(组合逻辑电路),c_wire,最后加上寄存器c自身的Tcu,整个过程时间的总和要小于一个小于一个时钟周期。

例如: Fclk = 20ns(一个时钟周期) Tsu = 1ns 则Tlut = 20 – 1 = 19ns.

上述结论的假设前提都是clk到达所有寄存器的的时间是完全一致的

下面来讨论clk到达每个寄存器时间不一样的情况

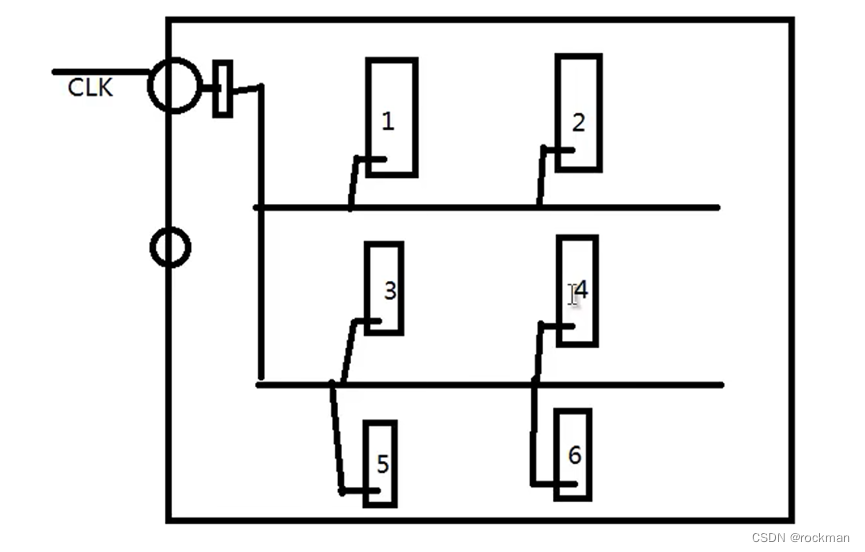

- 时钟树

时钟树,为了时钟到达各个寄存器之间的时间差距尽量小。

时钟偏斜(skew):时钟从源端口出发,到达目的寄存器和源寄存器的时间差值,如上模型clk到寄存器a和到寄存器c的时间差值。

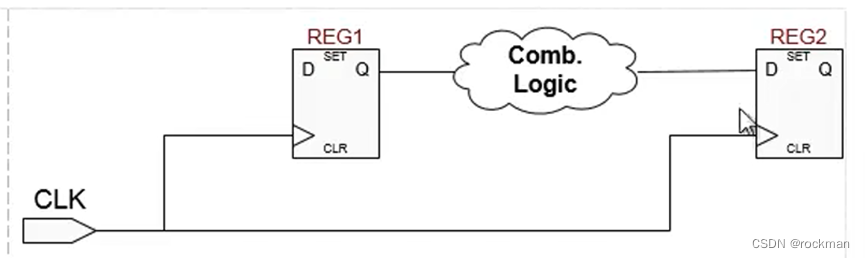

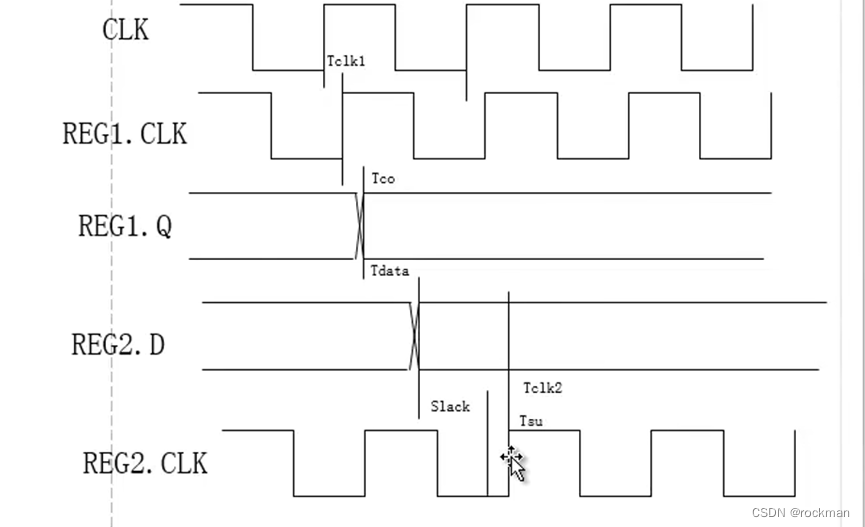

Tclk1(clock_delay):时钟信号从时钟源端口出来,到达源寄存器端口的时间

Tco:时钟上升沿到达寄存器的时钟端,到数据输出寄存器Q端口的时间

Tdata:数据从源寄存器Q端出发,到达目的寄存器D端的时间

Tclk:时钟周期

Tclk2:时钟信号从时钟源端口出发,到达目的寄存器时钟端口的时间

Tsu:寄存器要求的其数据端口的数据必须提前于时间上升沿到达时间的端口的时间(建立时间)

**目的寄存器能够正确的接受到源寄存器发送过来的数据满足的时序条件

Tclk1 + Tco + Tdata <= Tclk + Tclk2 – Tsu

Tclk + Tclk2 – Tsu -Tclk1 – Tco – Tdata >= 0

Tclk + (Tclk2 – Tclk1) -Tdata – Tco – Tsu >= 0

Slack = Tclk – Tskew – Tsu – Tco – Tdata >= 0

Slack = Tclk + Tskew – Tsu – Tco – Tdata >= 0,Tskew可正可负。

Slack:建立时间余量

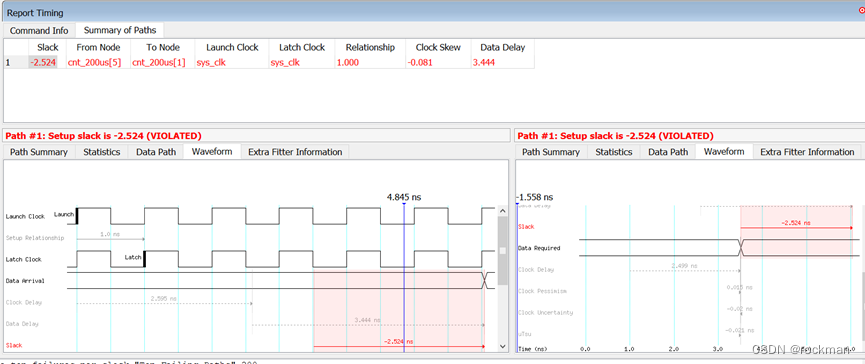

2、 基于timequest软件查看时序报告和基于RTL的逻辑时序优化的基本思路

在关键路径中插入寄存器来优化时序。

创建网表

Read SDC

查看时序报告

报告时钟

报告时钟最大频率

查看关键路径余量(余量最小路径)report top failing paths

Slack:建立时间余量

From node:源寄存器

To node:目的寄存器

Launch clock:源寄存器发射数据的时钟

Latch clock:目的寄存器接受数据的时钟

Relationship:launch clock edge 和latch clock edge的时间差

Cloc_skew: 时钟从源端口出发,到达目的寄存器和源寄存器的时间差值,加上时钟悲观

Clock_delay:源时钟到达寄存器的延迟

Data_delay: Tdata + Tco(经过Tclk1和data_delay到达目的寄存器端口)

uTsu:建立时间(cyclone iv负值是允许的)

clock pessimism:时钟悲观。就是源时钟到达目的寄存器走最短的路径,到源寄存器走最长的路径。也就是Tclk2按最小的来,Tclk1按最大的来。因为最终的目的是分析slack最小的路径。这样就会引出了一个矛盾,源时钟在传输的过程中,到达目的寄存器和源寄存器的开头有一段路径是重合的,与前者分析不一致,所以最终要补偿回去。该值会被算入

Clock_uncertainty:可以理解为时钟占空比不完全为理想占空比,时钟可能会提前或者延迟到来,提前到来会减小slack.

Tclk = 1ns

Tclk1=2.595ns

Tclk2=2.499ns

Tsu = -0.021ns

Data_delay = 3.444ns

Clock_pessimism = 0.015

Clock_uncertianty = -0.02

Tclk1 + data_delay(Tco+Tdata):数据到达时间

Tclk + Tclk2 – Tsu:数据需求时间

Tskew = Tclk2 -Tclk1 + clock_pessimsm

Slack = Tclk + Tskew – Tsu – Tco – Tdata + clock_uncertianty

Slack = Tclk + Tclk2 -Tclk1 + clock_pessimsm – Tsu – data_delay + clock_uncertianty

=1+2.499-2.595+0.015+0.021-3.444-0.02=-2.524

运算结果与上图一致

——总结于小梅哥FPGA时序分析和约束