DDR规格:

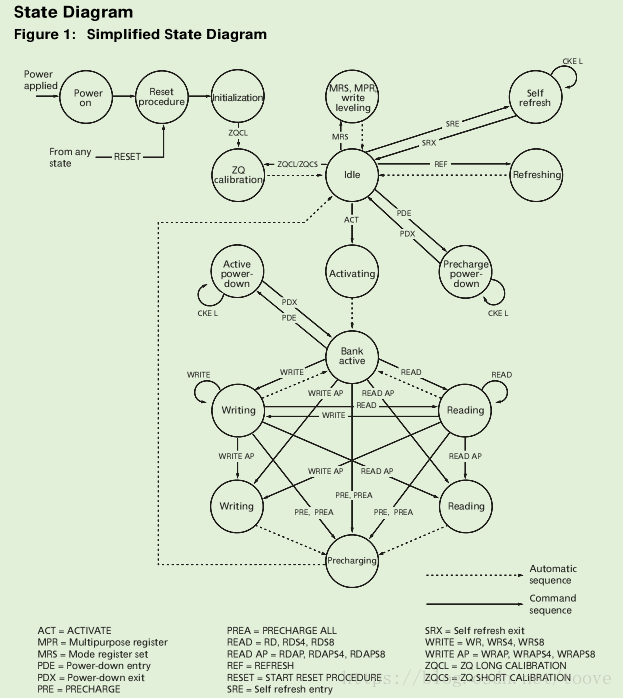

DDR工作状态图:

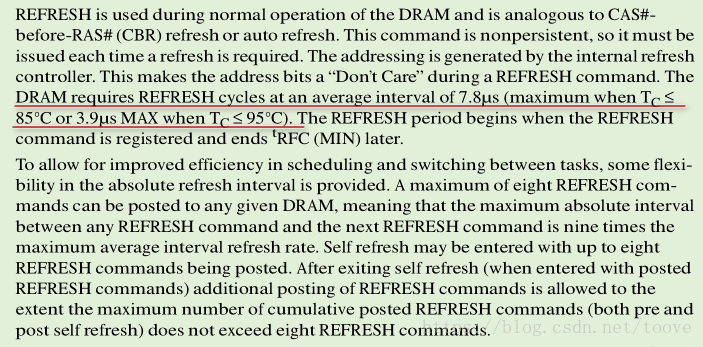

DDR 刷新描述:

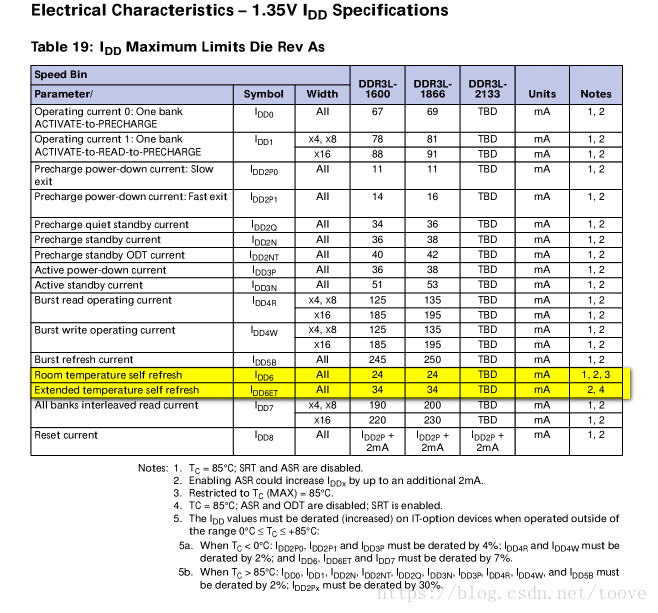

电特性:

工作模式简介:

1.1 自刷新模式(Self Refresh Mode)

DDR4 SDRAM中自刷新超市是用来保存存储阵列中的数据,即使在系统中其他的部分都已经断电的情况下,仍可以保持其功能。DRAM内部存在一个计数器来调整自刷新操作。在执行SRE命令之前,DRAM中的所有Bank都必须处于IDLE状态,即需要执行PRE ALL命令。SRE命令的定义是在时钟上升沿时,CS_n, RAS_n/A16, CAS_n/ A15以及CKE保持低电平,WE_n/A14与ACT_n保持高电平。既然有刷新,SDRAM中的数据是自然可以保持住的。SDRAM进入self refresh后,SDRAM controller也会disable输出到SDRAM的clock,从而整体的功耗都降低下来此模式中包含一种自动自刷新的机制,DRAM内含一个温度传感器,根据此传感器的数据,可自动选择刷新命令的间隔与周期。

1.2 断电模式(Power Down Mode)

在CKE是低电平的情况下,发送一个NOP或者INHIBIT命令就可以让SDRAM进入power down mode。Power Down有两种mode,一种叫做PRECHARGE POWER-DOWN,另外一种叫做ACTIVE POWER-DOWN。如果在所有bank都是idle状态下(没有打开的行)进入Power down mode,那么这种mode就叫做PRECHARGE POWER-DOWN(该状态的功耗大约是300uA)。如果在有打开行(active row)的情况下进入Power down mode,那么这种mode就叫做ACTIVE POWER-DOWN(该状态的功耗大约是6mA)。想让SDRAM芯片退出power down mode的时候,要拉高CKE信号,发送一个NOP或者INHIBIT命令就可以让SDRAM退出power down mode。为了进一步降低功耗,可以把SDRAM controller的clock输出disable掉(这时候CKE是disable的,即便是SDRAM controller产生了clock信号,SDRAM的内部逻辑电路也不会被驱动)。看起来一切都很美,问题来了,数据是否可以保持?很遗憾,超过了Refresh period(tREF)后,SDRAM中的数据就不会保持了。因此,为了保存数据,我们可以让SDRAM controller在auto refresh timer超时的时候退出power down mode,完成refresh的操作,之后,如果没有pending的数据,继续进入power down mode。

DDR4 DRAM中提供了一种功耗更加低的Maximum Power Down模式。通过配置MR4.A4=1来进入此模式。、Deep Power Down。SDRAM controller发送Deep Power Down命令可以将SDRAM芯片推送到一个极低功耗状态(约15uA)。这时候存储阵列的power会被shutdown,也就是意味着所有的数据是丢失掉了,这时候,mode register的设定是保持的。当从Deep Power Down退出的时候,需要对SDRAM芯片进行一个完整的初始化过程。

2 具体区别

2.1 数据保存

在SR模式中,是可以完全保证数据正确性的。而在PD模式中,PD模式持续的时间若果不大于9*tREFI,则DRAM可以保证数据的正确性。

2.2 时钟输入

在SR模式与Precharge PD模式中,控制器可在规定的时序范围内对时钟频率进行修改,或者关闭时钟。

2.3 进入方法

SR模式通过SRE命令进入,SRX命令退出。PD模式则是在DES命令下,将CKE信号拉低成低电平来进入,通过将CKE信号拉高成高电平来退出。

2.4 IO Buffer状态

在SR模式中,所有IO Buffer都处于打开状态。

在PD模式中,除了CK_t, CK_c, CKE与RESET_n的IO Buffer,其他所有的IO Buffer都是处于关闭状态的。

2.5 供电状态

这两种模式的供电都是处于有效状态的。

3 功耗的差别

SR模式 Act PD模式 Pre PD模式 Max PD

1mA 6mA 300uA 15uA

---------------------

作者:hierro_sic

来源:CSDN

原文:https://blog.csdn.net/hierro_zs/article/details/71158846

版权声明:本文为博主原创文章,转载请附上博文链接!

本文内容由网友自发贡献,版权归原作者所有,本站不承担相应法律责任。如您发现有涉嫌抄袭侵权的内容,请联系:hwhale#tublm.com(使用前将#替换为@)